Datasheet Summary

..

Version 2.10

THine

THC63LVDM63A/THC63LVDF64A

PRELIMINARY

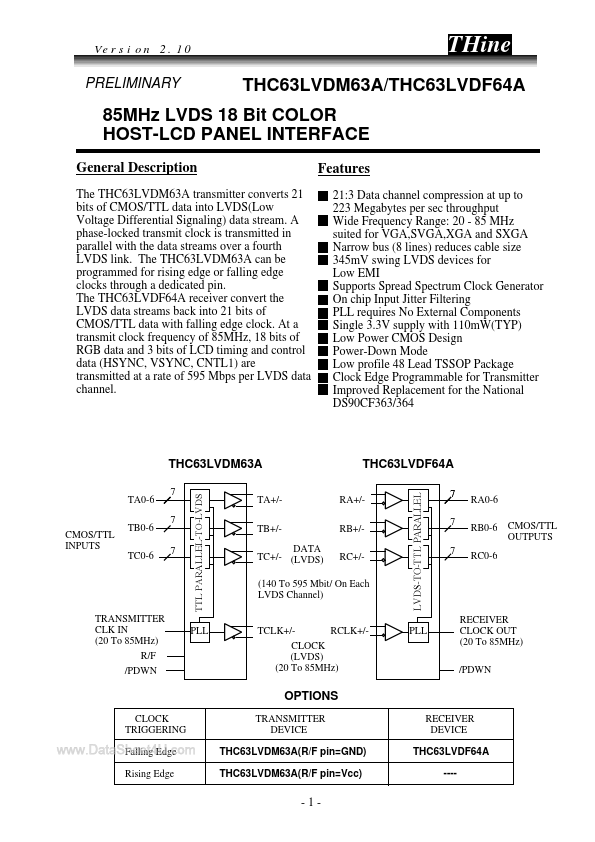

85MHz LVDS 18 Bit COLOR HOST-LCD PANEL INTERFACE

General Description

The THC63LVDM63A transmitter converts 21 bits of CMOS/TTL data into LVDS(Low Voltage Differential Signaling) data stream. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. The THC63LVDM63A can be programmed for rising edge or falling edge clocks through a dedicated pin. The THC63LVDF64A receiver convert the LVDS data streams back into 21 bits of CMOS/TTL data with falling edge clock. At a transmit clock frequency of 85MHz, 18 bits of RGB data and 3 bits of LCD timing and control data...