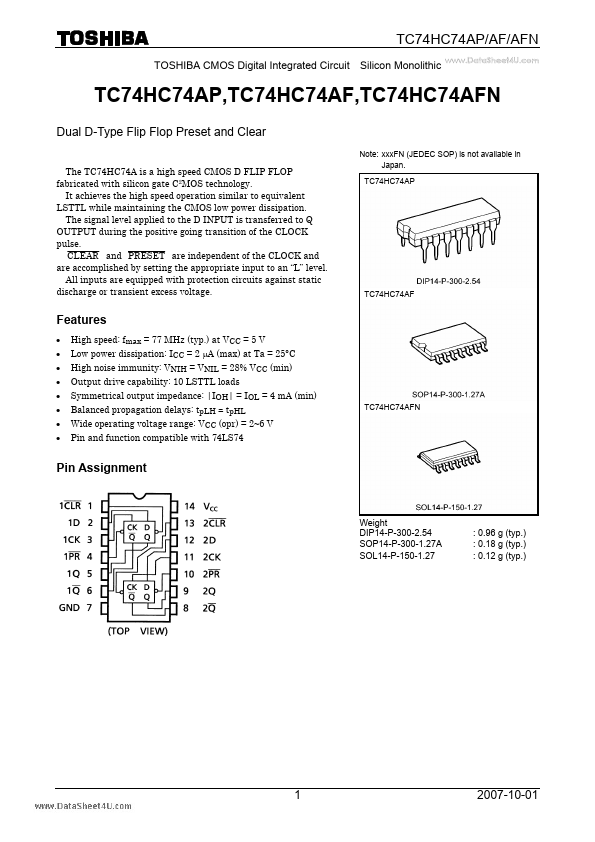

- Part: 74HC74AP

- Description: Dual D-Type Flip-Flop

- Manufacturer: Toshiba

- Size: 339.15 KB

Key Features

- High speed: fmax = 77 MHz (typ.) at VCC = 5 V Low power dissipation: ICC = 2 μA (max) at Ta = 25°C High noise immunity: VNIH = VNIL = 28% VCC (min) Output drive capability: 10 LSTTL loads Symmetrical output impedance: |IOH| = IOL = 4 mA (min) ∼ tpHL Balanced propagation delays: tpLH - Wide operating voltage range: VCC (opr) = 2~6 V Pin and function compatible with 74LS74

Datasheets by Manufacturer

- 74HC74AF — Toshiba — Dual D-Type Flip-Flop

- 74HC7403 — Philips Semiconductors — 4-Bit x 64-word FIFO register

- 74HC7404 — Philips Semiconductors — 5-Bit x 64-word FIFO register

- 74HC7030 — Philips Semiconductors — 9-bit x 64-word FIFO register

- 74HC7046A — Philips Semiconductors — Phase-locked-loop

- 74HC7080 — Philips Semiconductors — 16-bit even/odd parity generator/checker

- 74HC7597 — Philips Semiconductors — 8-bit shift register

- 74HC7540 — Nexperia — Octal Schmitt trigger buffer/line driver

- 74HC7541 — Nexperia — Octal Schmitt trigger buffer/line driver

- 74HC7014 — Nexperia — Hex non-inverting precision Schmitt-trigger