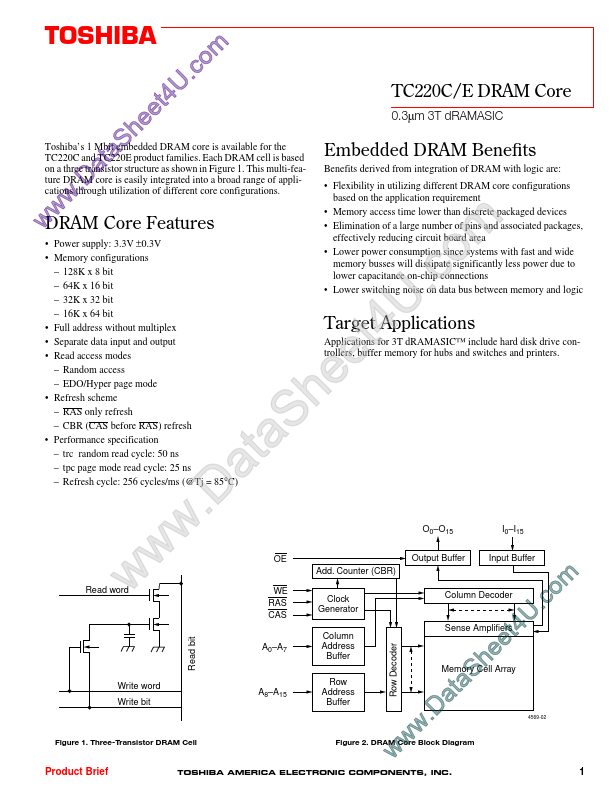

TC220C Overview

Key Features

- Power supply: 3.3V ±0.3V

- Memory configurations – 128K x 8 bit – 64K x 16 bit – 32K x 32 bit – 16K x 64 bit

- Full address without multiplex

- Separate data input and output

- Read access modes – Random access – EDO/Hyper page mode

- Refresh scheme – RAS only refresh – CBR (CAS before RAS) refresh

- Flexibility in utilizing different DRAM core configurations based on the application requirement

- Memory access time lower than discrete packaged devices

- Elimination of a large number of pins and associated packages, effectively reducing circuit board area

- Lower switching noise on data bus between memory and logic Target Applications Read word w w .D w Read bit t a S a OE e h