TH58NVG7D2GTA20 Key Features

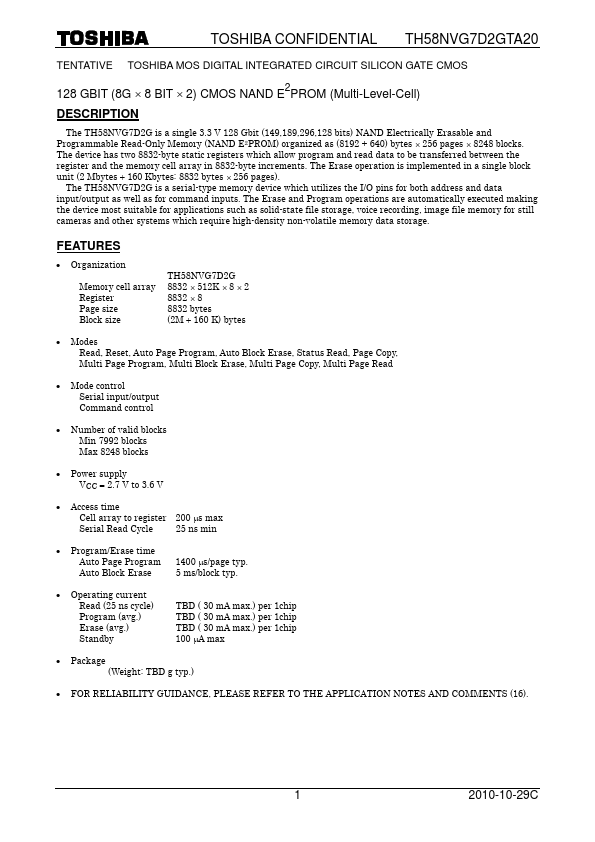

- Organization

- Modes Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase, M

- Mode control Serial input/output

- Number of valid blocks Min 7992 blocks Max 8248 blocks

- Power supply VCC 2.7 V to 3.6 V

- Access time

- Program/Erase time Auto Page Program

- Operating current Read (25 ns cycle) Program (avg.) Erase (avg.) Standby

- Package (Weight: TBD g typ.)

- FOR RELIABILITY GUIDANCE, PLEASE REFER TO THE APPLICATION NOTES AND MENTS (16)