TQ8016

TQ8016 is 1.3 Gigabit/sec 16x16 Digital ECL Crosspoint Switch manufactured by TriQuint Semiconductor.

Features

- >1.3 Gigabit/sec data rate

- Non-blocking architecture

- +200 ps delay match (one input to all outputs)

- ECL-level data inputs/outputs; CMOS-level control inputs

- Low crosstalk

- Fully differential data path

- Double row of output select latches minimizes reconfiguration time

- Available in 132-pin leaded chip carrier

For additional information and latest specifications, see our website: .triquint.

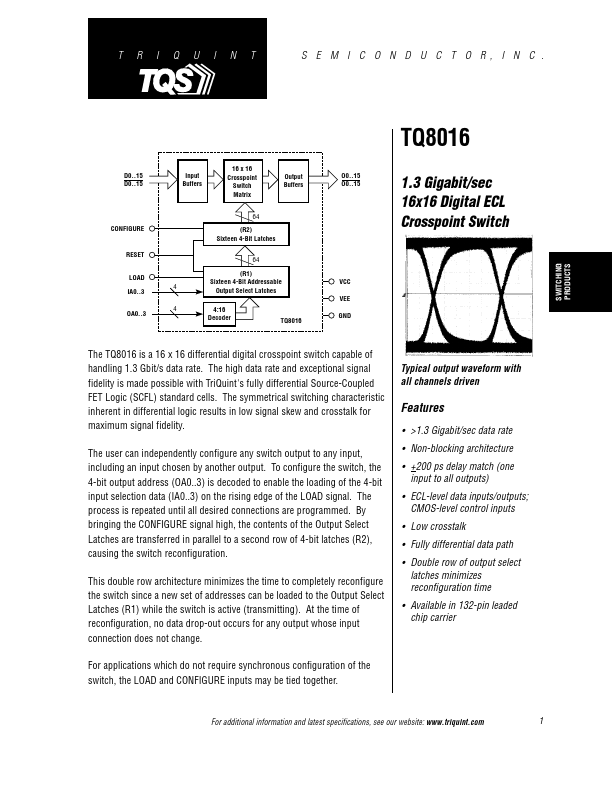

Figure 1. TQ8016 Architecture

16 X 1-BIT MULTIPLEXER

- .

DATA IN 0 (I0)

16 X 1-BIT MULTIPLEXER

Input Buffers

- .

DATA OUT 15 (O15) DATA OUT 0 (O0)

DATA IN 15 (I15)

CONFIGURE RESET LOAD 4:16 4 DECODE OUTPUT SELECT ADDRESS (OA0:3)

Configuration Register Program Register

INPUT ADDRESS (IA0:3)

Table 1. Pin Descriptions

Pin Name

D0- D15 D0- D15 D0- D15 O0- O15 O0- O15 IA0- IA3 OA0- OA3 CONFIGURE

Levels

ECL ECL ECL ECL ECL CMOS CMOS CMOS

Description

Differential Data Inputs Differential Data Inputs Differential Data Inputs Differential Data Outputs Differential Data Outputs Input Address Output Address Switch Reconfiguration

For additional information and latest specifications, see our website:...