TQ8103

TQ8103 is 622 Mb/s Clock & Data Recovery manufactured by TriQuint Semiconductor.

Features

- Single-chip CDR circuit for 622 Mb/s data

- Exceeds Bellcore and ITU jitter tolerance maps

- Single-ended ECL input has loopthrough path for external 50 ohm termination to minimize stubs and reflections

- Clock and data outputs are differential ECL

- Provides plete high-speed OC-12/STM-4 solution when used with TQ8101 or TQ8105 Mux/Demux/Framer/PLL

- External loop filter requires simple passive network

- Maintains clock in absence of data

- Transmission system transport cards

- Switch and cross-connect line cards

- ATM physical layer interfaces

- Test equipment

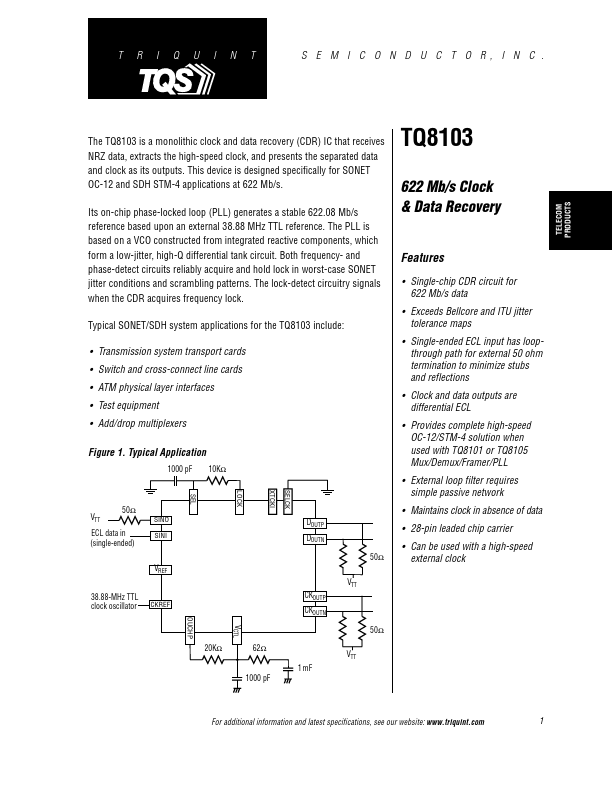

- Add/drop multiplexers Figure 1. Typical Application

1000 p F 10KΩ

SELCK XTCKI LOCK

50Ω

SINO SINI

DOUTP DOUTN 50Ω

ECL data in (single-ended)

- 28-pin leaded chip carrier

- Can be used with a high-speed external clock

VREF VTT 38.88-MHz TTL clock oscillator CKOUTP

CKREF

OUCHP

CKOUTN

V CTL

50Ω 62Ω 1 m F 1000 p F VTT

20KΩ

For additional information and latest specifications, see our website: .triquint.

Figure 2. TQ8103 Block Diagram

SELCK XTCKI SEL

SINO +16 SINI D Q VDD VREF VEE CKREF Frequency Detect

OUCHP V CTL

DOUTP DOUTN LOCK

Loc k Detect Phase Detect

CKOUTP Mux Charge Pump VCO CKOUTN

Functional Description

The TQ8103 CDR integrates separate detectors for acquiring frequency lock and maintaining precise phase lock. When the CDR is locked onto an ining NRZ data stream, its phase-detect circuitry pares the phase of the ining NRZ data and the phase of the generated 622.08 MHz clock. When they differ, the resulting error signal nulls the phase difference and puts the generated 622.08 MHz clock back in phase with the ining data. In this mode, the LOCK output is high. The phase-detect circuit operates only when the ining NRZ data transitions between states. SONET and SDH employ scrambling, which provides an average transition density of 50 percent; however, some data patterns can generate legitimate scrambled signals with a significant number of consecutive ones or...