SI6433BDQ Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 8

Max Operating Temp: 150 °C

Description

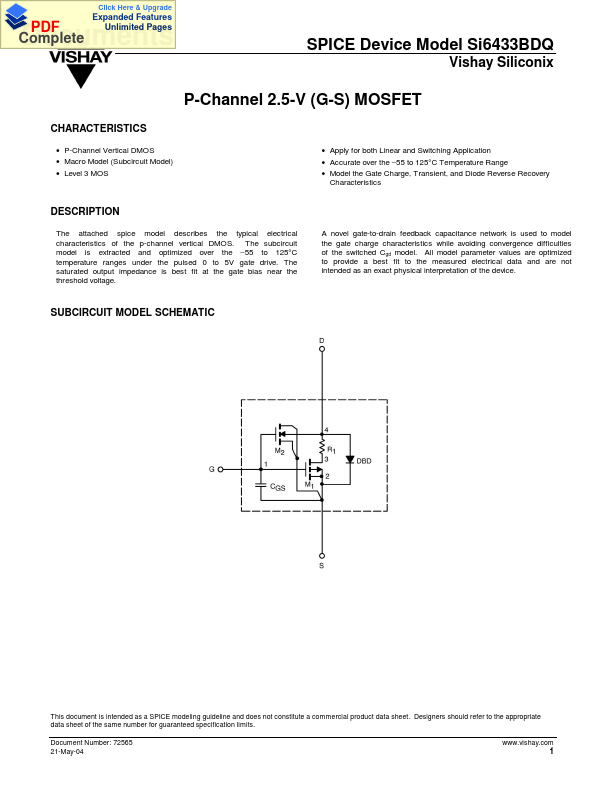

The attached spice model describes the typical SUBCIRCUIT MODEL SCHEMATIC This document is intended as a SPICE modeling guideline and does not constitute a commercial product data sheet. Designers should refer to the appropriate data sheet of the same number for guaranteed specification limits.

Key Features

- P-Channel Vertical DMOS

- Macro Model (Subcircuit Model)

- Apply for both Linear and Switching Application

- Accurate over the -55 to 125°C Temperature Range

- Model the Gate Charge, Transient, and Diode Reverse Recovery Characteristics