XC95288

XC95288 is XC95288 In-System Programmable CPLD manufactured by Xilinx.

Product Obsolete/Under Obsolescence

R XC95288 In-System Programmable CPLD

DS069 (v5.0) May 17, 2013

Features

- 15 ns pin-to-pin logic delays on all pins

- fCNT to 95 MHz

- 288 macrocells with 6,400 usable gates

- Up to 166 user I/O pins

- 5V in-system programmable

- Endurance of 10,000 program/erase cycles

- Program/erase over full mercial voltage and temperature range

- Enhanced pin-locking architecture

- Flexible 36V18 Function Block

- 90 product terms drive any or all of 18 macrocells within Function Block

- Global and product term clocks, output enables, set and reset signals

- Extensive IEEE Std 1149.1 boundary-scan (JTAG) support

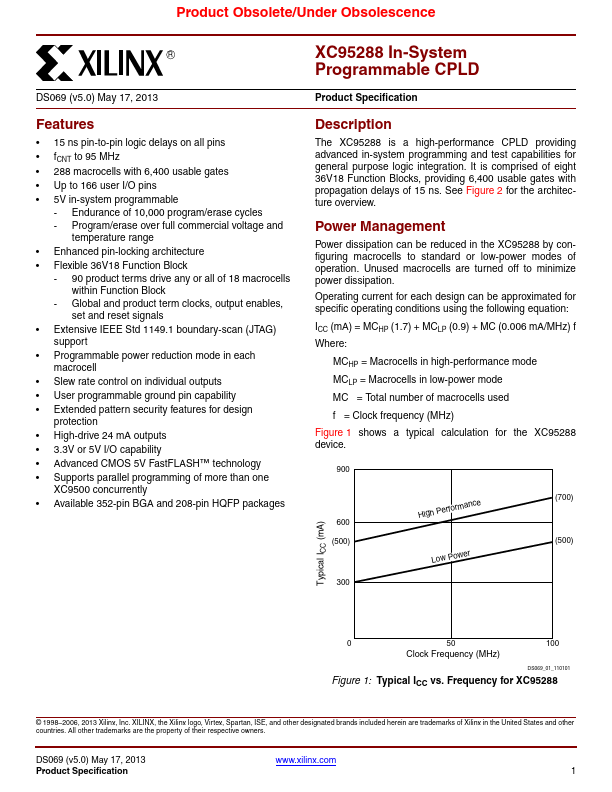

- Programmable power reduction mode in...