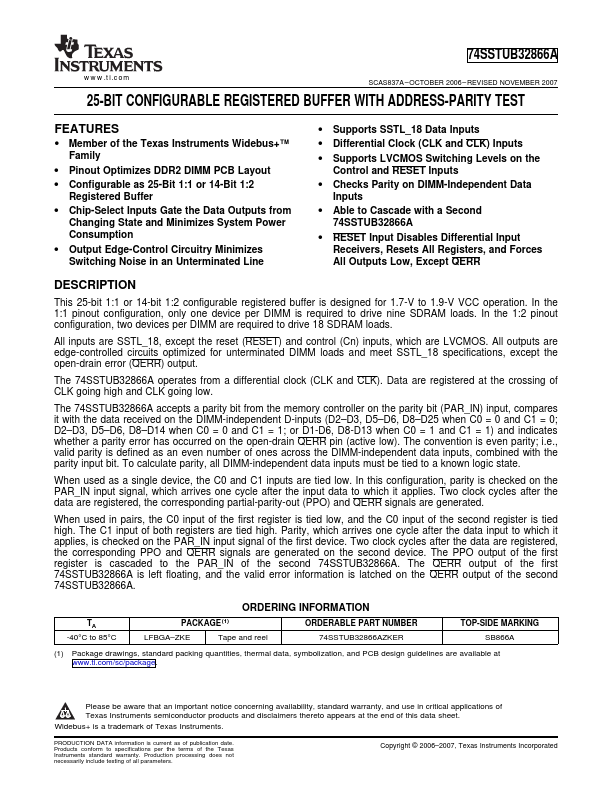

74SSTUB32866A

74SSTUB32866A is 25-Bit Configurable Registered Buffer manufactured by Texas Instruments.

.ti.

SCAS837A

- OCTOBER 2006

- REVISED NOVEMBER 2007

25-BIT CONFIGURABLE REGISTERED BUFFER WITH ADDRESS-PARITY TEST

Features

- 2 Member of the Texas Instruments Widebus+™ Family

- Pinout Optimizes DDR2 DIMM PCB Layout

- Configurable as 25-Bit 1:1 or 14-Bit 1:2

Registered Buffer

- Chip-Select Inputs Gate the Data Outputs from Changing State and Minimizes System Power Consumption

- Output Edge-Control Circuitry Minimizes Switching Noise in an Unterminated Line

- Supports SSTL_18 Data Inputs

- Differential Clock (CLK and CLK) Inputs

- Supports LVCMOS Switching Levels on the

Control and RESET Inputs

- Checks Parity on DIMM-Independent Data Inputs

- Able to Cascade with a Second 74SSTUB32866A

- RESET Input Disables Differential Input Receivers, Resets All Registers, and Forces All Outputs Low, Except QERR

DESCRIPTION

This 25-bit 1:1 or 14-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VCC operation. In the 1:1 pinout configuration, only one device per DIMM is required to drive nine SDRAM loads. In the 1:2 pinout configuration, two devices per DIMM are required to drive 18 SDRAM loads.

All inputs are SSTL_18, except the reset (RESET) and control (Cn) inputs, which are LVCMOS. All outputs are edge-controlled circuits optimized for unterminated DIMM loads and meet SSTL_18 specifications, except the open-drain error (QERR) output.

The 74SSTUB32866A operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low.

The 74SSTUB32866A accepts a parity bit from the memory controller on the parity bit (PAR_IN) input, pares it with the data received on the DIMM-independent D-inputs (D2- D3, D5- D6, D8- D25 when C0 = 0 and C1 = 0; D2- D3, D5- D6, D8- D14 when C0 = 0 and C1 = 1; or D1-D6, D8-D13 when C0 = 1 and C1 = 1) and indicates whether a parity error has occurred on the open-drain QERR pin (active low). The convention is even parity; i.e., valid parity is defined as an even...