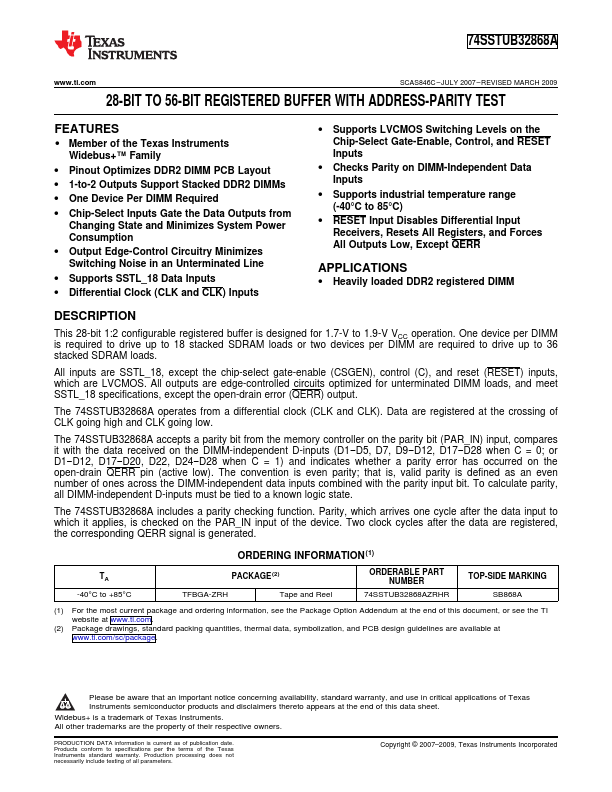

74SSTUB32868A

74SSTUB32868A is 28-Bit to 56-Bit Registered Buffer manufactured by Texas Instruments.

SCAS846C

- JULY 2007

- REVISED MARCH 2009

28-BIT TO 56-BIT REGISTERED BUFFER WITH ADDRESS-PARITY TEST

Features

- 23 Member of the Texas Instruments Widebus+™ Family

- Pinout Optimizes DDR2 DIMM PCB Layout

- 1-to-2 Outputs Support Stacked DDR2 DIMMs

- One Device Per DIMM Required

- Chip-Select Inputs Gate the Data Outputs from

Changing State and Minimizes System Power Consumption

- Output Edge-Control Circuitry Minimizes Switching Noise in an Unterminated Line

- Supports SSTL_18 Data Inputs

- Differential Clock (CLK and CLK) Inputs

- Supports LVCMOS Switching Levels on the Chip-Select Gate-Enable, Control, and RESET Inputs

- Checks Parity on DIMM-Independent Data Inputs

- Supports industrial temperature range (-40°C to 85°C)

- RESET Input Disables Differential Input Receivers, Resets All Registers, and Forces All Outputs Low, Except QERR

APPLICATIONS

- Heavily loaded DDR2 registered DIMM

DESCRIPTION

This 28-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VCC operation. One device per DIMM is required to drive up to 18 stacked SDRAM loads or two devices per DIMM are required to drive up to 36 stacked SDRAM loads.

All inputs are SSTL_18, except the chip-select gate-enable (CSGEN), control (C), and reset (RESET) inputs, which are LVCMOS. All outputs are edge-controlled circuits optimized for unterminated DIMM loads, and meet SSTL_18 specifications, except the open-drain error (QERR) output.

The 74SSTUB32868A operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low.

The 74SSTUB32868A accepts a parity bit from the memory controller on the parity bit (PAR_IN) input, pares it with the data received on the DIMM-independent D-inputs (D1- D5, D7, D9- D12, D17- D28 when C = 0; or D1- D12, D17- D20, D22, D24- D28...