ADS6243

ADS6243 is Analog-to-Digital Converters manufactured by Texas Instruments.

- Part of the ADS6242 comparator family.

- Part of the ADS6242 comparator family.

FEATURES

- Maximum Sample Rate: 125 MSPS

- 14-Bit Resolution with No Missing Codes

- Simultaneous Sample and Hold

- 3.5 d B Coarse Gain and up to 6 d B

Programmable Fine Gain for SFDR/SNR Trade Off

- Serialized LVDS Outputs with Programmable Internal Termination Option

- Supports Sine, LVCMOS, LVPECL, LVDS Clock Inputs and Amplitude down to 400 m Vpp

- Internal Reference with External Reference Support

- No External Decoupling Required for References

- 3.3-V Analog and Digital Supply

- 48 QFN Package (7 mm × 7 mm)

- Pin patible 12-Bit Family (ADS622X SLAS543A)

- Feature patible Quad Channel Family (ADS644X

- SLAS531A and ADS642X SLAS532A)

APPLICATIONS

- Base-Station IF Receivers

- Diversity Receivers

- Medical Imaging

- Test Equipment

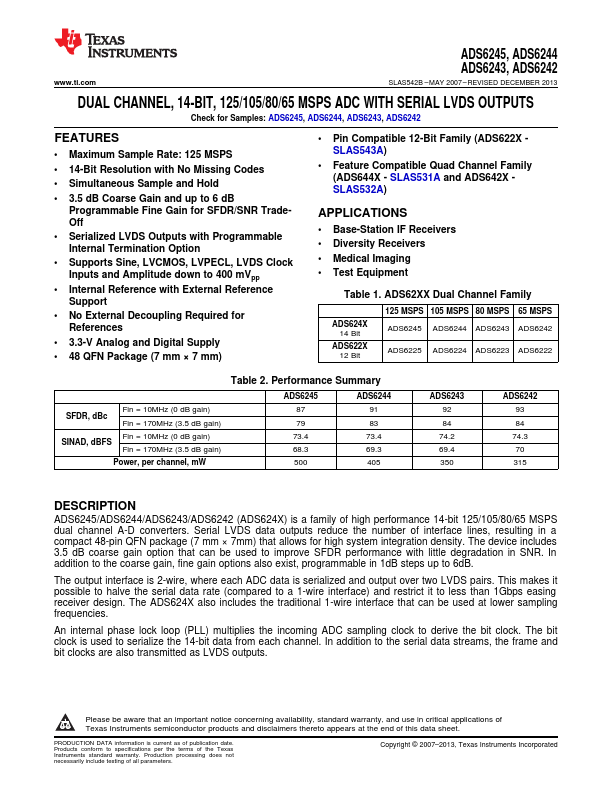

Table 1. ADS62XX Dual Channel Family

ADS624X 14 Bit

ADS622X 12 Bit

125 MSPS 105 MSPS 80 MSPS 65 MSPS ADS6245 ADS6244 ADS6243 ADS6242 ADS6225 ADS6224 ADS6223 ADS6222

Table 2. Performance Summary

SFDR, d Bc

Fin = 10MHz (0 d B gain) Fin = 170MHz (3.5 d B gain)

Fin = 10MHz (0 d B gain) SINAD, d BFS

Fin = 170MHz (3.5 d B gain)

Power, per channel, m W

ADS6245 87 79 73.4 68.3 500

ADS6244 91 83 73.4 69.3 405

ADS6243 92 84 74.2 69.4 350

ADS6242 93 84 74.3 70 315

DESCRIPTION

ADS6245/ADS6244/ADS6243/ADS6242 (ADS624X) is a family of high performance 14-bit 125/105/80/65 MSPS dual channel A-D converters. Serial LVDS data outputs reduce the number of interface lines, resulting in a pact 48-pin QFN package (7 mm × 7mm) that allows for high system integration density. The device includes 3.5 d B coarse gain option that can be used to improve SFDR performance with little degradation in SNR. In addition to the coarse gain, fine gain options also exist, programmable in 1d B steps up to 6d B.

The output interface is 2-wire, where each ADC data is serialized and output over two LVDS pairs. This makes it possible to halve the serial data rate (pared to a 1-wire interface) and restrict it to less than 1Gbps easing receiver design. The ADS624X also...