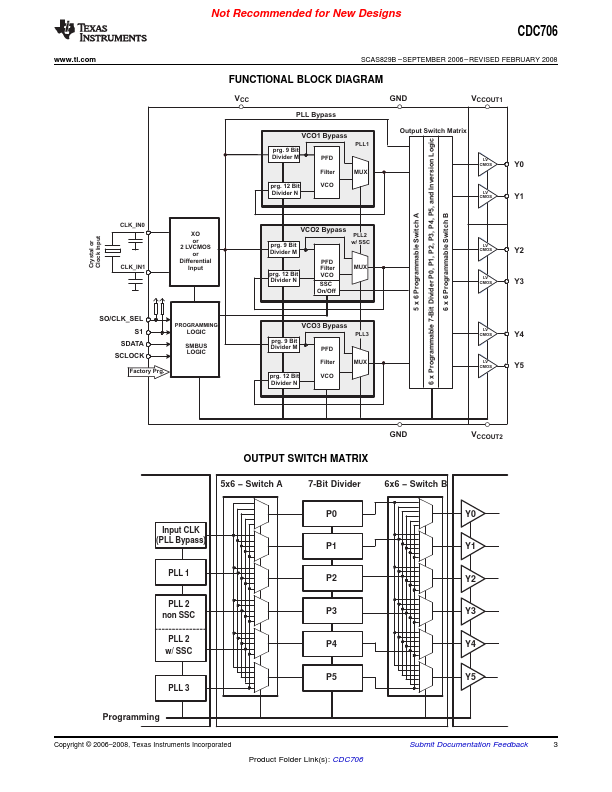

CDC706 Description

Not Remended for New Designs CDC706 .ti....................................................................................................................................... SCAS829B SEPTEMBER 2006 REVISED FEBRUARY 2008 PROGRAMMABLE 3-PLL CLOCK SYNTHESIZER / MULTIPLIER / DIVIDER Check for Samples:.

CDC706 Key Features

- 2 High Performance 3:6 PLL Based Clock Synthesizer / Multiplier / Divider

- User Programmable PLL Frequencies

- Easy In-Circuit Programming via SMBus Data Interface

- Wide PLL Divider Ratio Allows 0-PPM Output Clock Error

- Clock Inputs Accept a Crystal or a Single-Ended LVCMOS or a Differential Input Signal

- Accepts Crystal Frequencies from 8 MHz up to 54 MHz

- Accepts LVCMOS or Differential Input Frequencies up to 200 MHz

- Two Programmable Control Inputs [S0/S1] for User Defined Control Signals

- Six LVCMOS Outputs with Output Frequencies up to 300 MHz

- LVCMOS Outputs can be Programmed for plementary Signals