CDCLVD2108

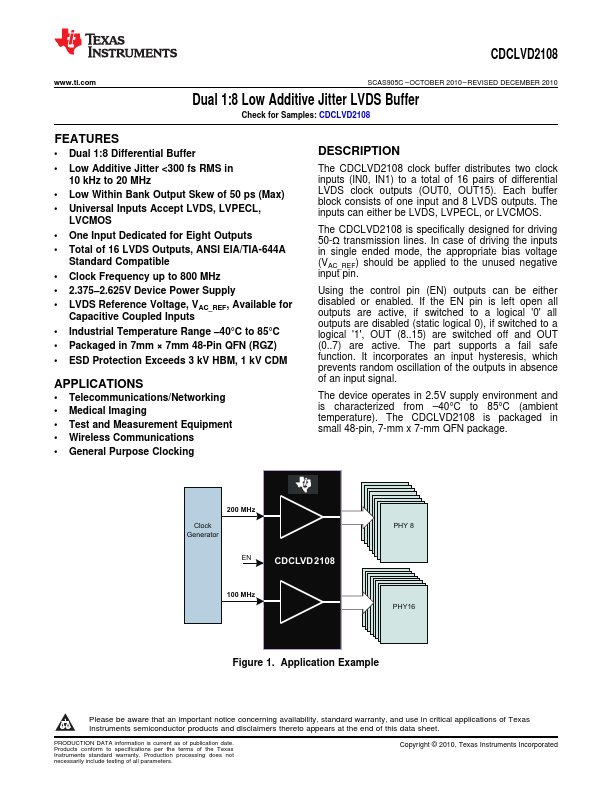

CDCLVD2108 is Dual 1:8 Low Additive Jitter LVDS Buffer manufactured by Texas Instruments.

.ti.

SCAS905C

- OCTOBER 2010

- REVISED DECEMBER 2010

Dual 1:8 Low Additive Jitter LVDS Buffer

Check for Samples: CDCLVD2108

Features

- Dual 1:8 Differential Buffer

- Low Additive Jitter <300 fs RMS in

10 k Hz to 20 MHz

- Low Within Bank Output Skew of 50 ps (Max)

- Universal Inputs Accept LVDS, LVPECL,

LVCMOS

- One Input Dedicated for Eight Outputs

- Total of 16 LVDS Outputs, ANSI EIA/TIA-644A

Standard patible

- Clock Frequency up to 800 MHz

- 2.375- 2.625V Device Power Supply

- LVDS Reference Voltage, VAC_REF, Available for

Capacitive Coupled Inputs

- Industrial Temperature Range

- 40°C to 85°C

- Packaged in 7mm × 7mm 48-Pin QFN (RGZ)

- ESD Protection Exceeds 3 k V HBM, 1 k V CDM

APPLICATIONS

- Telemunications/Networking

- Medical Imaging

- Test and Measurement Equipment

- Wireless munications

- General Purpose...