CDCM9102 Overview

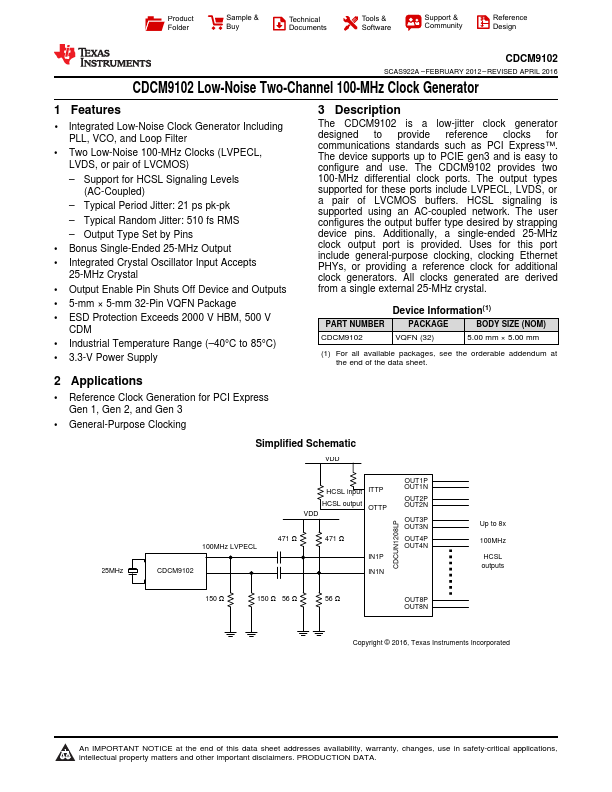

The CDCM9102 is a low-jitter clock generator designed to provide reference clocks for munications standards such as PCI Express™. The device supports up to PCIE gen3 and is easy to configure and use. The CDCM9102 provides two 100-MHz differential clock ports.

CDCM9102 Key Features

- 1 Integrated Low-Noise Clock Generator Including PLL, VCO, and Loop Filter

- Two Low-Noise 100-MHz Clocks (LVPECL, LVDS, or pair of LVCMOS)

- Support for HCSL Signaling Levels (AC-Coupled)

- Typical Period Jitter: 21 ps pk-pk

- Typical Random Jitter: 510 fs RMS

- Output Type Set by Pins

- Bonus Single-Ended 25-MHz Output

- Integrated Crystal Oscillator Input Accepts

- Output Enable Pin Shuts Off Device and Outputs

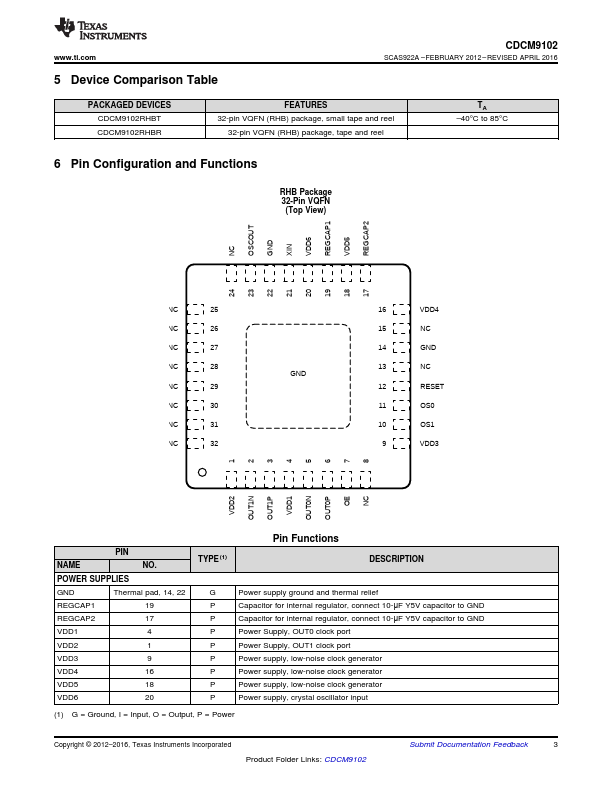

- 5-mm × 5-mm 32-Pin VQFN Package

CDCM9102 Applications

- Reference Clock Generation for PCI Express Gen 1, Gen 2, and Gen 3