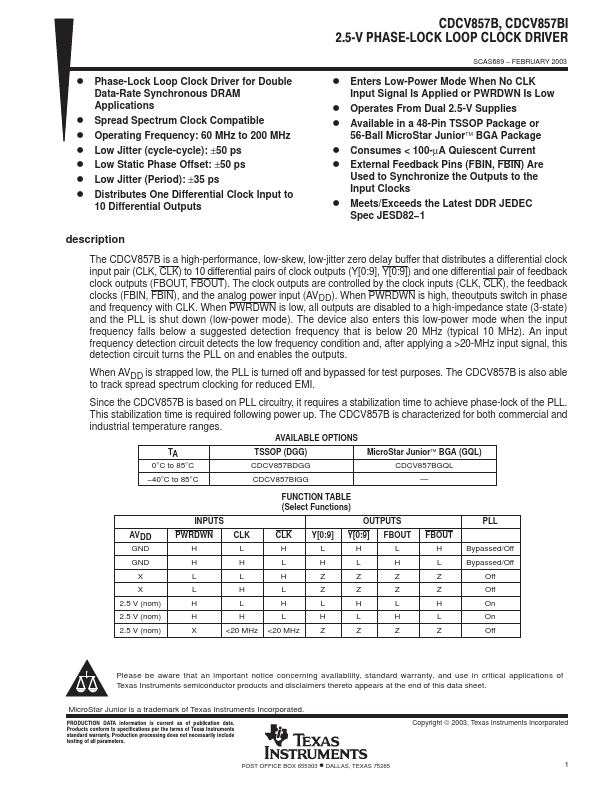

CDCV857B Overview

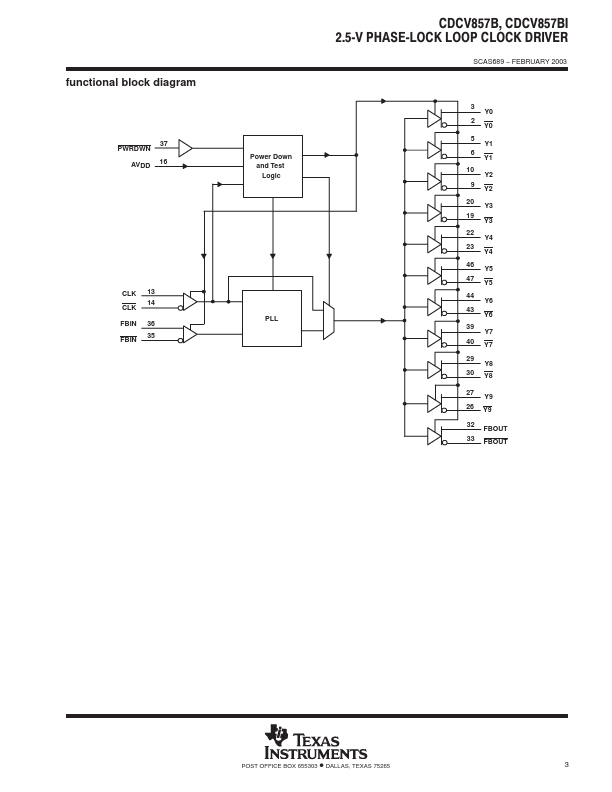

The CDCV857B is a high-performance, low-skew, low-jitter zero delay buffer that distributes a differential clock input pair (CLK, CLK) to 10 differential pairs of clock outputs (Y[0:9], Y[0:9]) and one differential pair of feedback clock outputs (FBOUT, FBOUT). The clock outputs are controlled by the clock inputs (CLK, CLK), the feedback clocks (FBIN, FBIN), and the analog power input (AVDD). When PWRDWN is high,...