LP2998

Features

- 1 AEC-Q100 Test Guidance with the following results (SO Power PAD-8):

- Device HBM ESD Classification Level H1C

- Junction Temperature Range

- 40°C to 125°C

- 1.35 V Minimum VDDQ

- Source and Sink Current

- Low Output Voltage Offset

- No External Resistors Required

- Linear Topology

- Suspend to Ram (STR) Functionality

- Low External ponent Count

- Thermal Shutdown

2 Applications

- DDR1, DDR2, DDR3, and DDR3L Termination Voltage

- Automotive Infotainment

- FPGA

- Industrial/Medical PC

- SSTL-18, SSTL-2, and SSTL-3 Termination

- HSTL Termination

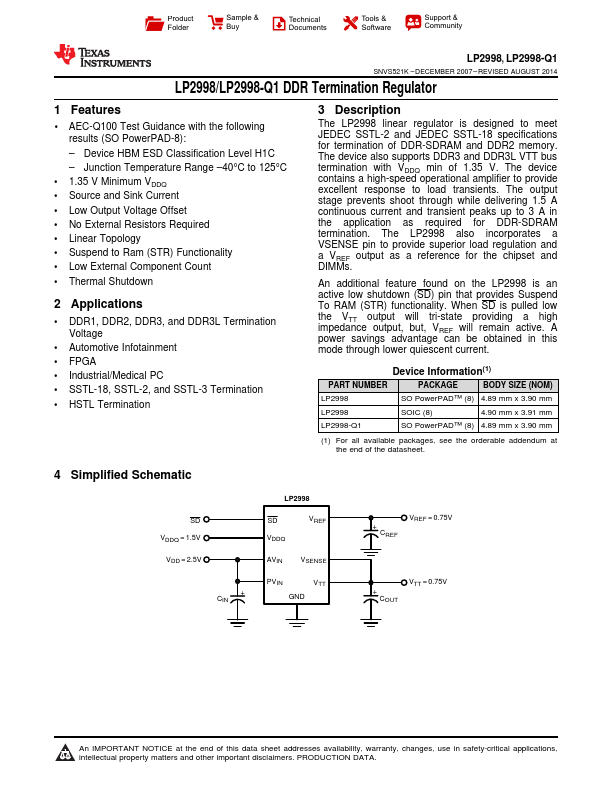

3 Description

The LP2998 linear regulator is designed to meet JEDEC SSTL-2 and JEDEC SSTL-18 specifications for termination of DDR-SDRAM and DDR2 memory. The device also supports DDR3 and DDR3L VTT bus termination with VDDQ min of 1.35 V. The device contains a high-speed operational amplifier to provide excellent response to load transients. The output stage prevents shoot through while delivering 1.5 A continuous current and transient...