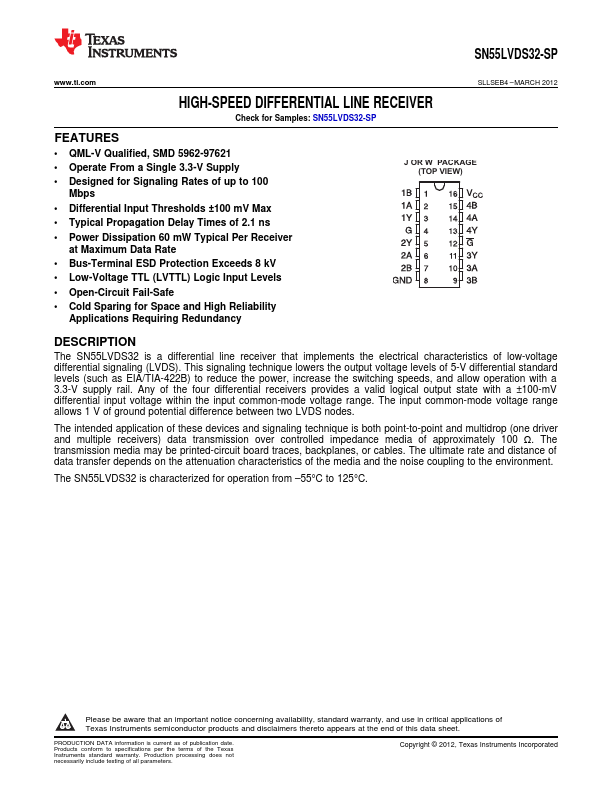

SN55LVDS32-SP Overview

Description

The SN55LVDS32 is a differential line receiver that implements the The intended application of these devices and signaling technique is both point-to-point and multidrop (one driver and multiple receivers) data transmission over controlled impedance media of approximately 100 Ω. The transmission media may be printed-circuit board traces, backplanes, or cables.

Key Features

- QML-V Qualified, SMD 5962-97621

- Operate From a Single 3.3-V Supply

- Designed for Signaling Rates of up to 100 Mbps

- Differential Input Thresholds ±100 mV Max

- Typical Propagation Delay Times of 2.1 ns