SN55LVDS32 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

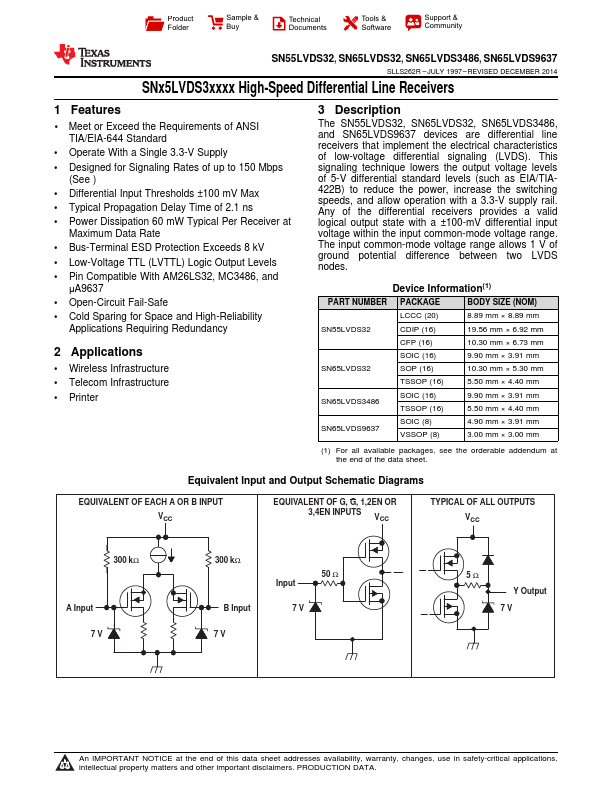

The SN55LVDS32, SN65LVDS32, SN65LVDS3486, and SN65LVDS9637 devices are differential line receivers that implement the Device Information(1) PART NUMBER PACKAGE BODY SIZE (NOM) LCCC (20) 8.89 mm × 8.89 mm SN55LVDS32 CDIP (16) 19.56 mm × 6.92 mm CFP (16) 10.30 mm × 6.73 mm SOIC (16) 9.90 mm × 3.91 mm SN65LVDS32 SOP (16) 10.30 mm × 5.30 mm TSSOP (16) 5.50 mm × 4.40 mm SN65LVDS3486 SOIC (16) TSSOP (16) 9.90 mm × 3.91 mm 5.50 mm × 4.40 mm SN65LVDS9637 SOIC (8) VSSOP (8) 4.90 mm × 3.91 mm.

Key Features

- 1 Meet or Exceed the Requirements of ANSI TIA/EIA-644 Standard

- Operate With a Single 3.3-V Supply

- Designed for Signaling Rates of up to 150 Mbps (See )

- Differential Input Thresholds ±100 mV Max

- Typical Propagation Delay Time of 2.1 ns