SN65LV1224A Overview

Key Specifications

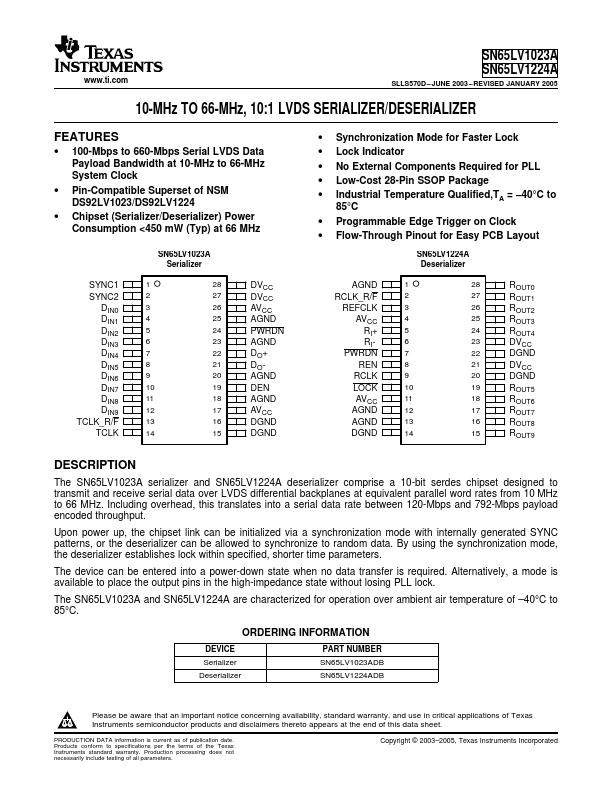

Package: SSOP

Mount Type: Surface Mount

Pins: 28

Operating Voltage: 3.3 V

Description

The SN65LV1023A serializer and SN65LV1224A deserializer comprise a 10-bit serdes chipset designed to transmit and receive serial data over LVDS differential backplanes at equivalent parallel word rates from 10 MHz to 66 MHz. Including overhead, this translates into a serial data rate between 120-Mbps and 792-Mbps payload encoded throughput.

Key Features

- 100-Mbps to 660-Mbps Serial LVDS Data Payload Bandwidth at 10-MHz to 66-MHz System Clock

- Pin-Compatible Superset of NSM DS92LV1023/DS92LV1224

- Synchronization Mode for Faster Lock

- Lock Indicator

- No External Components Required for PLL