SN65LVDS86A-Q1

SN65LVDS86A-Q1 is Receiver manufactured by Texas Instruments.

FEATURES

- 2 3:21 Data Channel Expansion at up to 178.5 Mbytes/s Throughput

- Suited for SVGA, XGA, or SXGA Display Data Transmission From Controller to Display With Very Low EMI

- Three Data Channels and Clock Low-Voltage Differential Channels In and 21 Data and Clock Low-Voltage TTL Channels Out

- Operates From a Single 3.3-V Supply

- Tolerates 4-k V Human-Body Model (HBM) ESD

- Packaged in Thin Shrink Small-Outline

Package (TSSOP) With 20-Mil Terminal Pitch

- Consumes Less Than 1 m W When Disabled

- Wide Phase-Lock Input Frequency Range

31 MHz to 68 MHz

- No External ponents Required for PLL

- Inputs Meet or Exceed the Standard

Requirements of ANSI EIA/TIA-644 Standard

- Improved Replacement for the SN75LVDS86 and NSC DS90C364

- Improved Jitter Tolerance

- Qualified for Automotive Applications

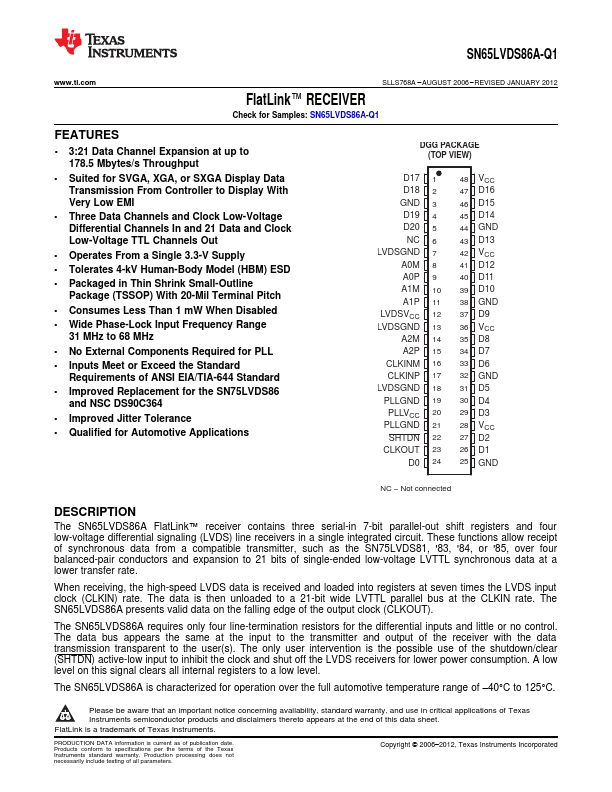

DGG PACKAGE (TOP VIEW)

D17 1 D18 2 GND 3 D19 4 D20 5 NC 6 LVDSGND 7 A0M 8 A0P 9 A1M 10 A1P 11 LVDSVCC 12 LVDSGND 13 A2M 14 A2P 15 CLKINM 16 CLKINP 17 LVDSGND 18 PLLGND 19 PLLVCC 20 PLLGND 21 SHTDN 22 CLKOUT 23

D0 24

48 VCC 47 D16 46 D15 45 D14 44 GND 43 D13 42 VCC 41 D12 40 D11 39 D10 38 GND 37 D9 36 VCC 35 D8 34 D7 33 D6 32 GND 31 D5 30 D4 29 D3 28 VCC 27 D2 26 D1 25 GND

- Not connected

DESCRIPTION

The SN65LVDS86A Flat Link™ receiver contains three serial-in 7-bit parallel-out shift registers and four low-voltage differential signaling (LVDS) line receivers in a single integrated circuit. These functions allow receipt of synchronous data from a patible transmitter, such as the SN75LVDS81, '83, '84, or '85, over four balanced-pair conductors and expansion to 21 bits of single-ended low-voltage LVTTL synchronous data at a lower transfer rate.

When receiving, the high-speed LVDS data is received and loaded into registers at seven times the LVDS input clock (CLKIN) rate. The data is then unloaded to a 21-bit wide LVTTL parallel bus at the CLKIN rate. The SN65LVDS86A presents valid data on the falling edge of the output clock (CLKOUT).

The SN65LVDS86A requires only...