SN65MLVD048 Overview

Key Specifications

Package: VQFN

Pins: 48

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

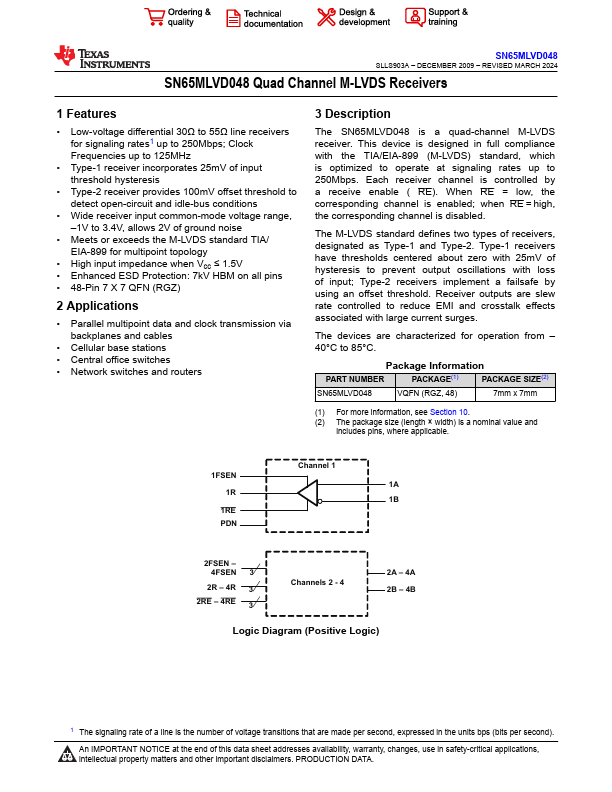

The SN65MLVD048 is a quad-channel M-LVDS receiver. This device is designed in full compliance with the TIA/EIA-899 (M-LVDS) standard, which is optimized to operate at signaling rates up to 250Mbps.

Key Features

- Low-voltage differential 30Ω to 55Ω line receivers for signaling rates1 up to 250Mbps; Clock Frequencies up to 125MHz

- Type-1 receiver incorporates 25mV of input threshold hysteresis

- Type-2 receiver provides 100mV offset threshold to detect open-circuit and idle-bus conditions

- Wide receiver input common-mode voltage range, –1V to 3.4V, allows 2V of ground noise

- Meets or exceeds the M-LVDS standard TIA/ EIA-899 for multipoint topology