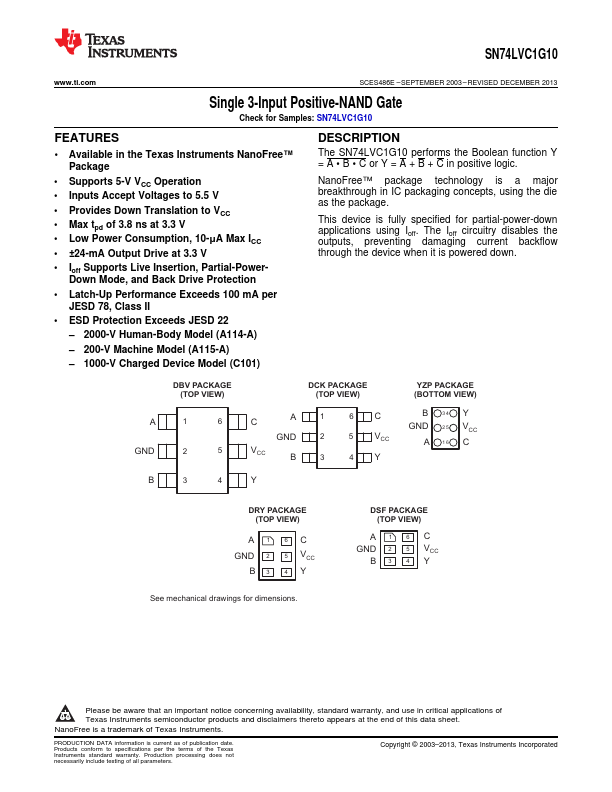

SN74LVC1G10 Overview

Key Specifications

Package: SOT-23

Mount Type: Surface Mount

Pins: 6

Max Voltage (typical range): 5.5 V

Description

The SN74LVC1G10 performs the Boolean function Y = A - B - C or Y = A + B + C in positive logic. NanoFree™ package technology is a major breakthrough in IC packaging concepts, using the die as the package.

Key Features

- 2 Available in the Texas Instruments NanoFree™ Package

- Supports 5-V VCC Operation

- Inputs Accept Voltages to 5.5 V

- Provides Down Translation to VCC

- Max tpd of 3.8 ns at 3.3 V