SN75LVDS86A Overview

Key Specifications

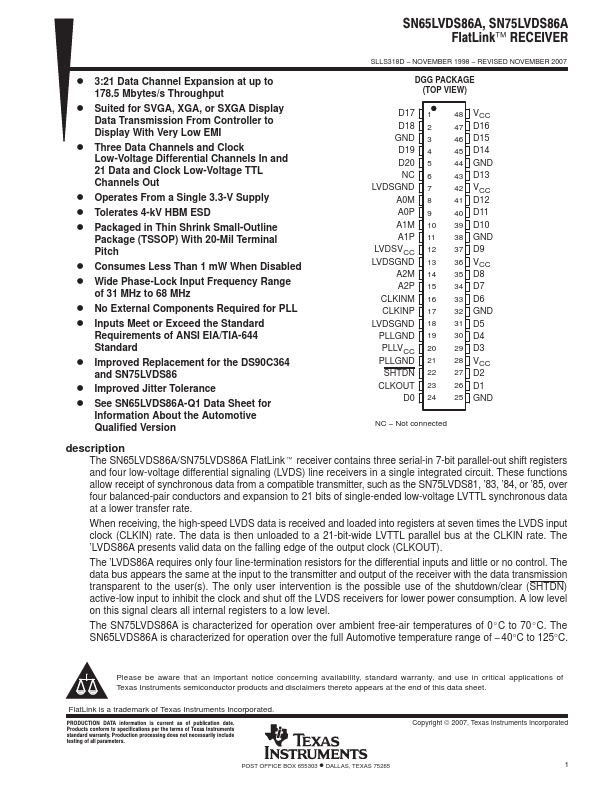

Package: TSSOP

Pins: 48

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

The SN65LVDS86A/SN75LVDS86A FlatLinkt receiver contains three serial-in 7-bit parallel-out shift registers and four low-voltage differential signaling (LVDS) line receivers in a single integrated circuit. These functions allow receipt of synchronous data from a compatible transmitter, such as the SN75LVDS81, ’83, ’84, or ’85, over four balanced-pair conductors and expansion to 21 bits of single-ended low-voltage LVTTL synchronous data at a lower transfer rate.