TMS320TCI6486 Overview

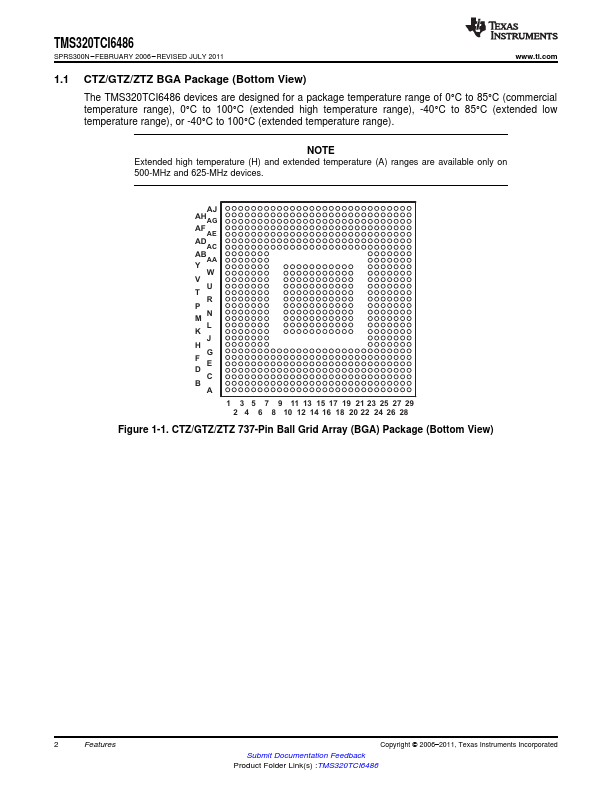

SPRS300N FEBRUARY 2006 REVISED JULY 2011 TMS320TCI6486 munications Infrastructure Digital Signal Processor.

TMS320TCI6486 Key Features

- Six On-Chip TMS320C64x+ Megamodules

- Endianess: Little Endian, Big Endian

- C64x+ Megamodule Main Features

- High-Performance, Fixed-Point TMS320C64x+ DSP

- 500/625/700 MHz

- Eight 32-Bit Instructions/Cycle

- 4000 MIPS/MMACS (16-Bits) at 500 MHz

- Dedicated SPLOOP Instruction

- pact Instructions (16-Bit)

- Instruction Set Enhancements