TMS320TCI6489 Overview

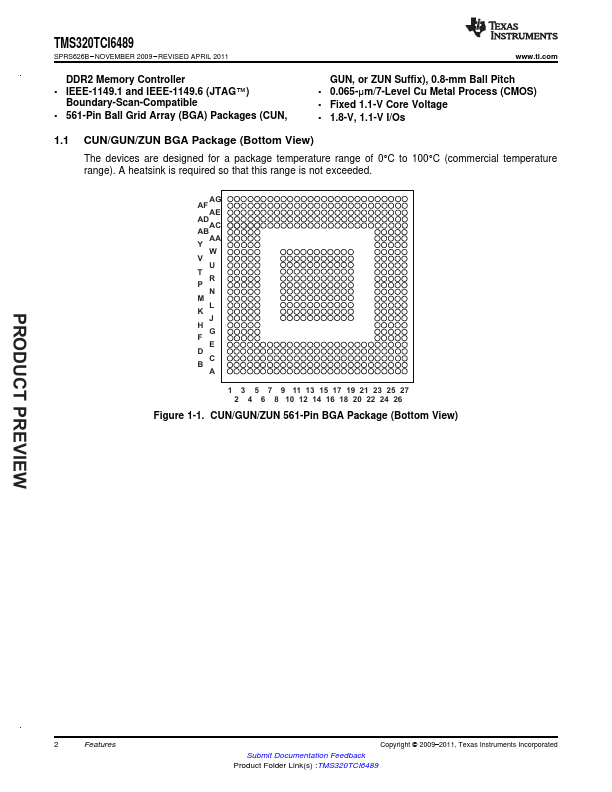

SPRS626B NOVEMBER 2009 REVISED APRIL 2011 TMS320TCI6489 munications Infrastructure Digital Signal Processor PRODUCT PREVIEW.

TMS320TCI6489 Key Features

- Key Features

- High-Performance munications Infrastructure DSP (TCI6489)

- 1.18-ns Instruction Cycle Time

- 850-MHz Clock Rate

- 0°C to 100°C mercial Temperature

- 3 TMS320C64x+™ DSP Cores; Six RSAs for CDMA Processing (2 per core)

- One Receive Accelerator (RAC)

- Enhanced VCP2/TCP2

- Frame Synchronization Interface

- 16-/32-Bit DDR2-667 Memory Controller