TPIC6B259

TPIC6B259 is POWER LOGIC 8-BIT ADDRESSABLE LATCH manufactured by Texas Instruments.

description

S1 8 GND 9

13 G 12 S2

This power logic 8-bit addressable latch controls

GND 10 11 GND open-drain DMOS-transistor outputs and is designed for general-purpose storage

- No internal connection applications in digital systems. Specific uses

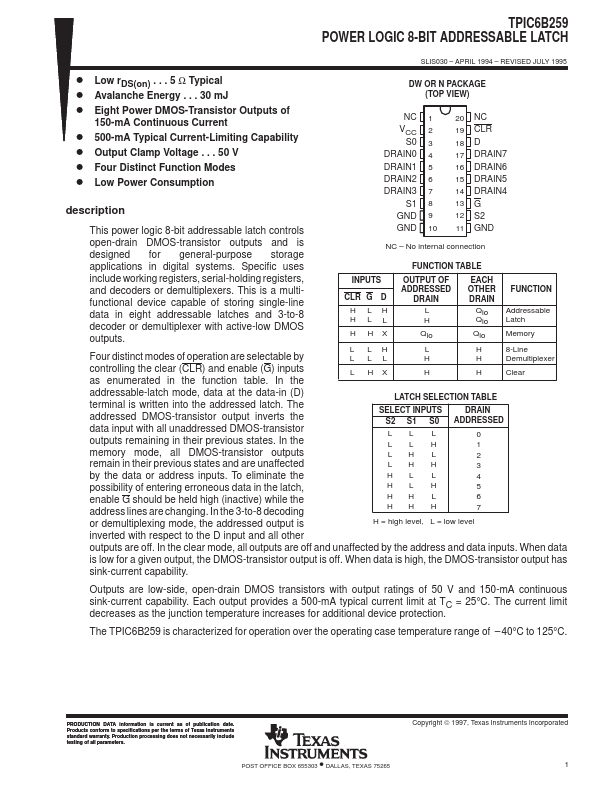

FUNCTION TABLE include working registers, serial-holding registers, and decoders or demultiplexers. This is a multifunctional device capable of storing single-line data in eight addressable latches and 3-to-8 decoder or demultiplexer with active-low DMOS outputs.

INPUTS

CLR G D H LH HLL H HX

OUTPUT OF ADDRESSED

DRAIN L H

Qio

EACH OTHER DRAIN

Qio Qio

Qio

FUNCTION

Addressable Latch Memory

Four distinct modes of operation are selectable by controlling the clear (CLR) and enable (G) inputs as enumerated in the function table. In the

L LH

L LL

L HX

8-Line

Demultiplexer

Clear addressable-latch mode, data at the data-in (D) terminal is written into the addressed latch. The addressed DMOS-transistor output inverts the data input with all unaddressed DMOS-transistor outputs remaining in their previous states. In the memory mode, all DMOS-transistor outputs remain in their previous states and are unaffected by the data or address inputs. To eliminate the possibility of entering erroneous data in the latch, enable G should be held high (inactive) while the address lines are changing. In the 3-to-8 decoding or demultiplexing mode, the addressed output is

LATCH SELECTION TABLE

SELECT INPUTS S2 S1 S0

LL L LLH LH L LHH HL L HL H HH L HH H

DRAIN ADDRESSED

0 1 2 3 4 5 6 7

H = high level, L = low level inverted with respect to the D input and all other outputs are off. In the clear mode, all outputs are off and unaffected by the address and data inputs. When data is low for a given output, the DMOS-transistor output is off. When data is high, the DMOS-transistor output has sink-current capability.

Outputs are low-side, open-drain DMOS transistors with output ratings of 50 V and 150-m A...