TPIC6C596

TPIC6C596 is Power Logic 8-Bit Shift Register manufactured by Texas Instruments.

Features

- 1 Low RDS(on), 7 Ω (Typical)

- Avalanche Energy, 30 m J

- Eight Power DMOS Transistor Outputs of 100-m A

Continuous Current

- 250-m A Current Limit Capability

- ESD Protection, 2500 V

- Output Clamp Voltage, 33 V

- Enhanced Cascading for Multiple Stages

- All Registers Cleared With Single Input

- Low Power Consumption

2 Applications

- Instrumentation Clusters

- Tell-Tale Lamps

- LED Illumination and Controls

- Automotive Relay or Solenoids Drivers

G8 RCK 10

7 CLR

15 SRCK

2 SER IN

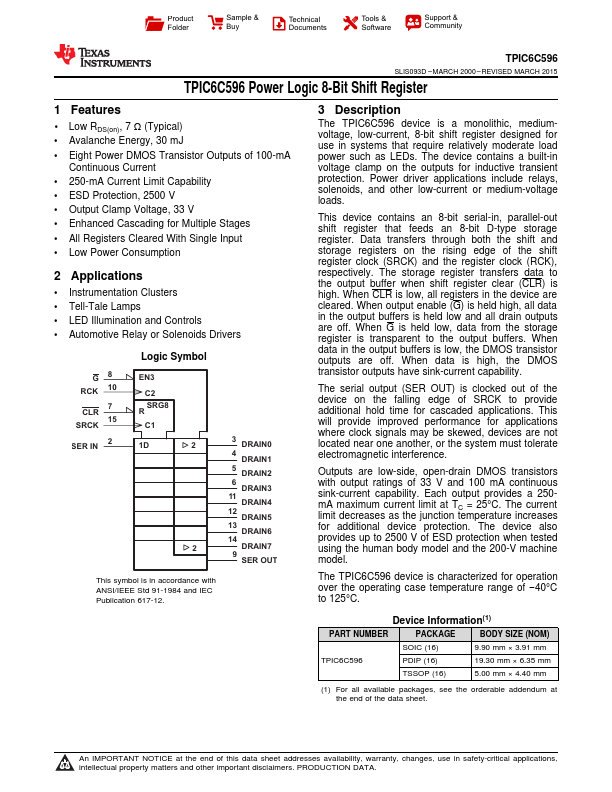

Logic Symbol

EN3 C2 SRG8

R C1

1D

3 DRAIN0

4 DRAIN1

5 DRAIN2

6 DRAIN3

11 DRAIN4

12 DRAIN5

13 DRAIN6

14 DRAIN7

9 SER OUT

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

3 Description

The TPIC6C596 device is a monolithic, mediumvoltage, low-current, 8-bit shift register designed for use in systems that require relatively moderate load power such as LEDs. The device contains a built-in voltage clamp on the outputs for inductive transient protection. Power driver applications include relays, solenoids, and other low-current or medium-voltage loads.

This device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Data transfers through both the shift and storage registers on the rising edge of the shift register clock (SRCK) and the register clock (RCK), respectively. The storage register transfers data to the output buffer when shift register clear (CLR) is high. When CLR is low, all registers in the device are cleared. When output enable (G) is held high, all data in the output buffers is held low and all drain outputs are off. When G is held low, data from the storage register is transparent to the output buffers. When data in the output buffers is low, the DMOS transistor outputs are off. When data is high, the DMOS transistor outputs have sink-current capability.

The serial output (SER OUT) is clocked out of the device on the falling edge of SRCK to provide additional hold time for...