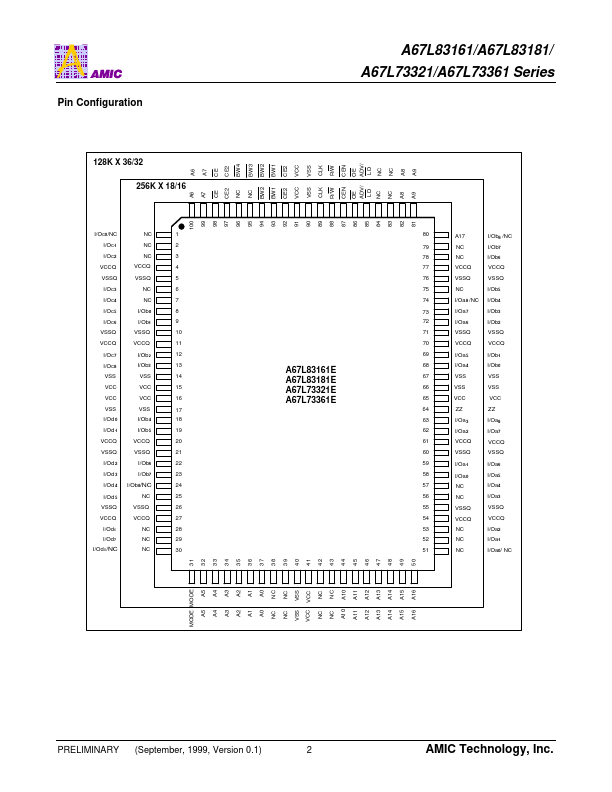

A67L73361 Description

The AMIC Direct Bus Alternation™ (DBA™) SRAM family employs high-speed, low-power CMOS designs using an advanced CMOS process. These SRAMs are optimized for 100 percent bus utilization without the insertion of any wait cycles during WriteRead alternation. The positive edge triggered single clock input (CLK) controls all synchronous inputs passing through the registers.