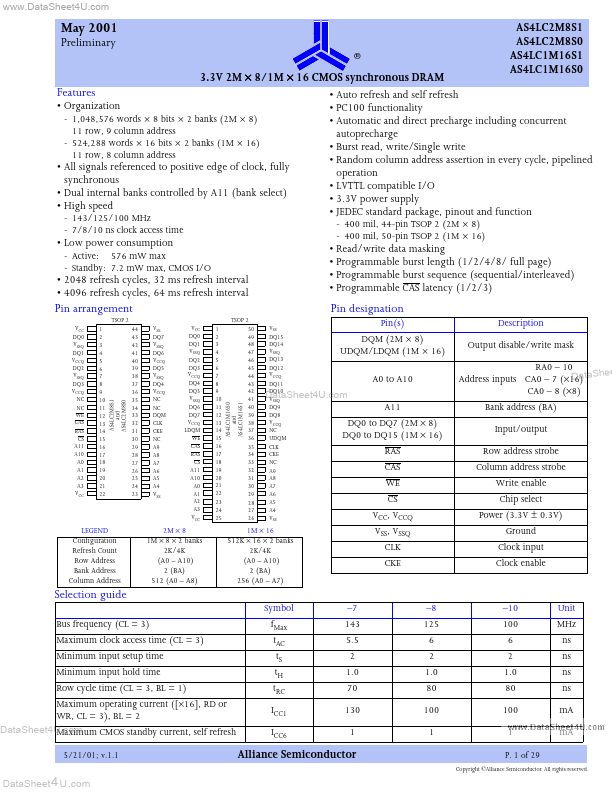

AS4LC2M8S1

AS4LC2M8S1 is (AS4LCxMxxSx) 3.3V 2M X 8/1M X 16 CMOS synchronous DRAM manufactured by Alliance Semiconductor.

- Part of the AS4LC2M8S0 comparator family.

- Part of the AS4LC2M8S0 comparator family.

..

May 2001

Preliminary

®

3.3V 2M × 8/1M × 16 CMOS synchronous DRAM Features

- Organization

- 1,048,576 words × 8 bits × 2 banks (2M × 8) 11 row, 9 column address

- 524,288 words × 16 bits × 2 banks (1M × 16) 11 row, 8 column address

AS4LC2M8S1 AS4LC2M8S0 AS4LC1M16S1 AS4LC1M16S0

- All signals referenced to positive edge of clock, fully synchronous

- Dual internal banks controlled by A11 (bank select)

- High speed

- 143/125/100 MHz

- 7/8/10 ns clock access time

- Auto refresh and self refresh

- PC100 functionality

- Automatic and direct precharge including concurrent autoprecharge

- Burst read, write/Single write

- Random column address assertion in every cycle,...