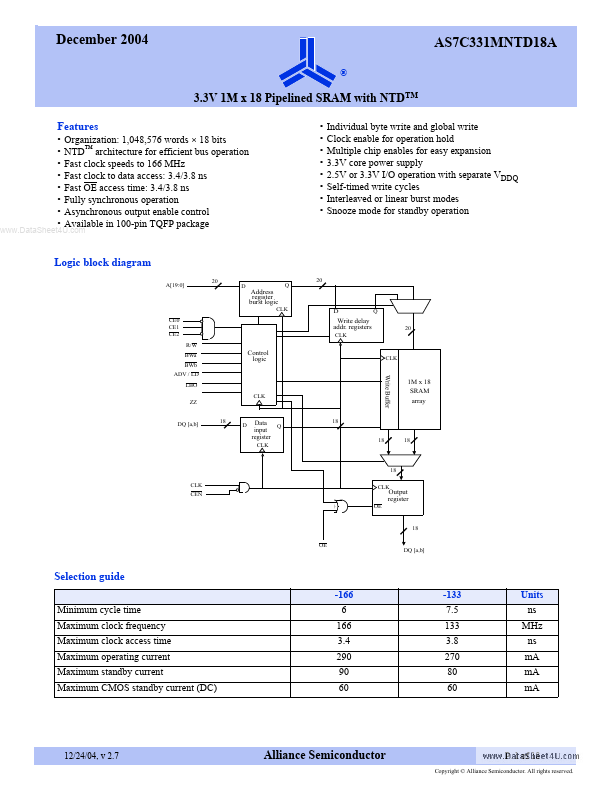

AS7C331MNTD18A Key Features

- Individual byte write and global write Clock enable for operation hold Multiple chip enables for easy expansion 3.3V cor

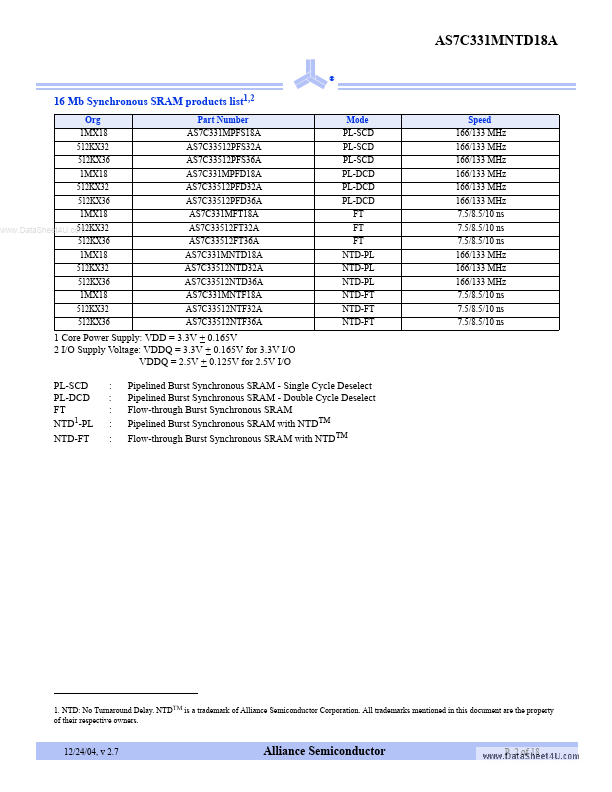

- Single Cycle Deselect Pipelined Burst Synchronous SRAM

- Double Cycle Deselect Flow-through Burst Synchronous SRAM Pipelined Burst Synchronous SRAM with NTDTM Flow-through Burst

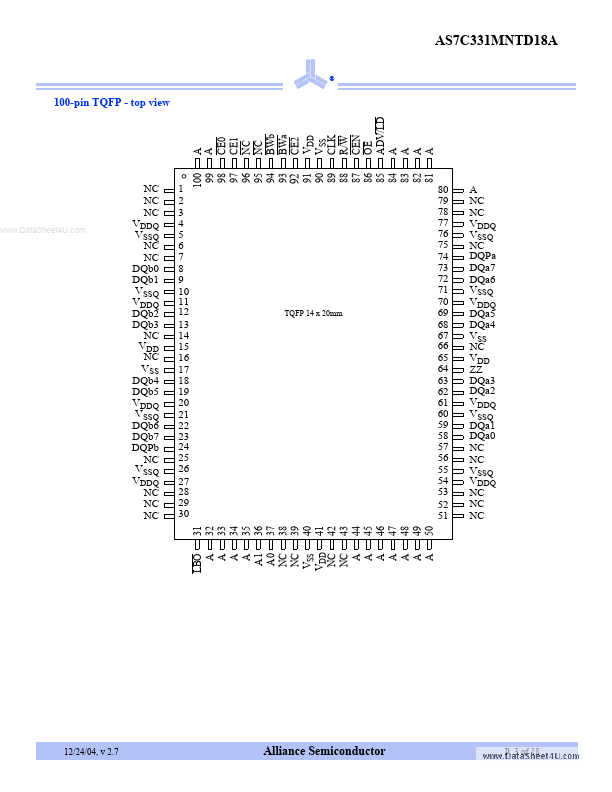

- top view