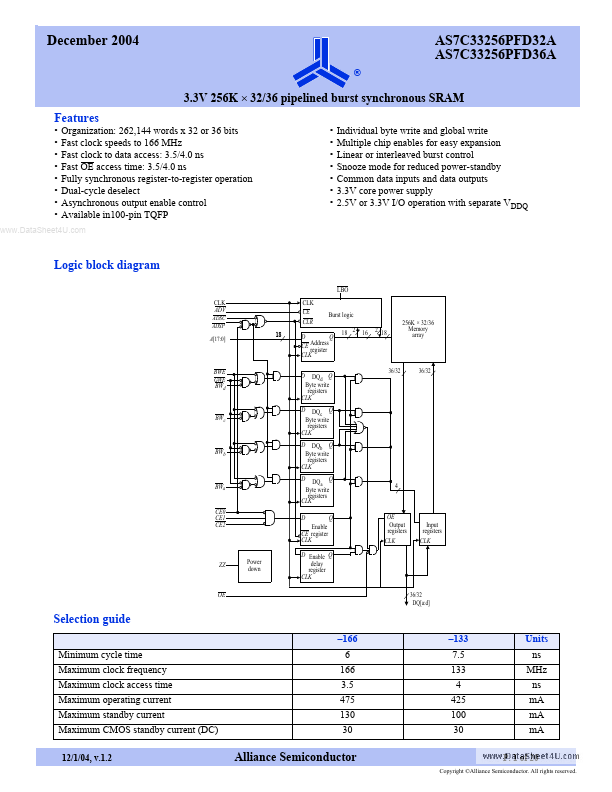

AS7C33256PFD32A Key Features

- Individual byte write and global write Multiple chip enables for easy expansion Linear or interleaved burst control Snoo

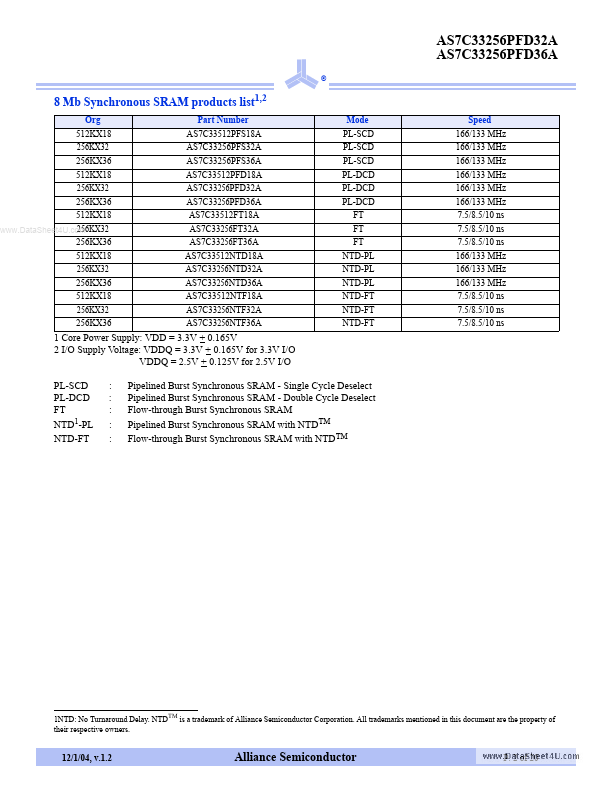

- 166 Minimum cycle time Maximum clock frequency Maximum clock access time Maximum operating current Maximum standby curre

- 133 7.5 133 4 425 100 30

- Single Cycle Deselect Pipelined Burst Synchronous SRAM

- Double Cycle Deselect Flow-through Burst Synchronous SRAM Pipelined Burst Synchronous SRAM with NTDTM Flow-through Burst