ADSP-21992

ADSP-21992 is Mixed Signal DSP Controller manufactured by Analog Devices.

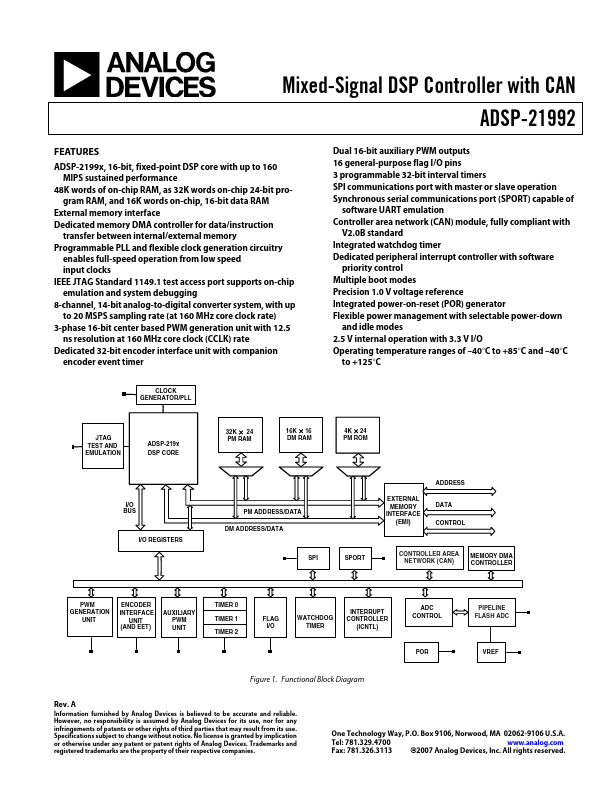

Mixed-Signal DSP Controller with CAN ADSP-21992

Features

ADSP-2199x, 16-bit, fixed-point DSP core with up to 160 MIPS sustained performance

48K words of on-chip RAM, as 32K words on-chip 24-bit program RAM, and 16K words on-chip, 16-bit data RAM

External memory interface Dedicated memory DMA controller for data/instruction transfer between internal/external memory Programmable PLL and flexible clock generation circuitry enables full-speed operation from low speed input clocks IEEE JTAG Standard 1149.1 test access port supports on-chip emulation and system debugging 8-channel, 14-bit analog-to-digital converter system, with up to 20 MSPS sampling rate (at 160 MHz core clock rate) 3-phase...