| Part | CY14B104N |

|---|---|

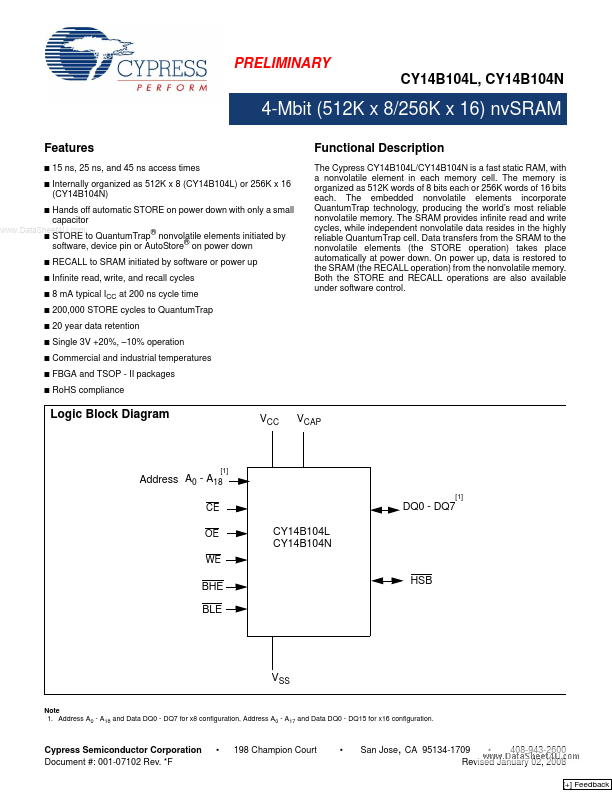

| Description | 4-Mbit (512K x 8/256K x 16) nvSRAM |

| Manufacturer | Cypress |

| Size | 710.92 KB |

Pricing from 60.4044 USD, available from Avnet and Rochester Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Avnet | 129 | 12+ : 60.4044 USD 24+ : 59.5584 USD 48+ : 58.7124 USD 96+ : 57.8664 USD |

View Offer |

| Avnet | 0 | 270+ : 38.0303 USD 540+ : 36.5486 USD 1080+ : 35.0669 USD 2160+ : 33.5852 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CY14E512I | Cypress | 512-Kbit (64 K x 8) Serial (I2C) nvSRAM |

| CY14B512Q | Cypress | 512-Kbit (64K x 8) SPI nvSRAM |

| CY14E064I | Cypress | 64-Kbit (8 K x 8) Serial (I2C) nvSRAM |