CY26200

Features

- Integrated phase-locked loop (PLL)

- Low-jitter, high-accuracy outputs

- 3.3V operation Part Number CY26200 Outputs 1 Input Frequency Range 19.44 MHz Benefits

- High-performance PLL tailored for T1/E1 clock generation

- Meets critical timing requirements in plex system designs

- Enables application patibility Output Frequencies 1.544 MHz/2.048 MHz (selectable)

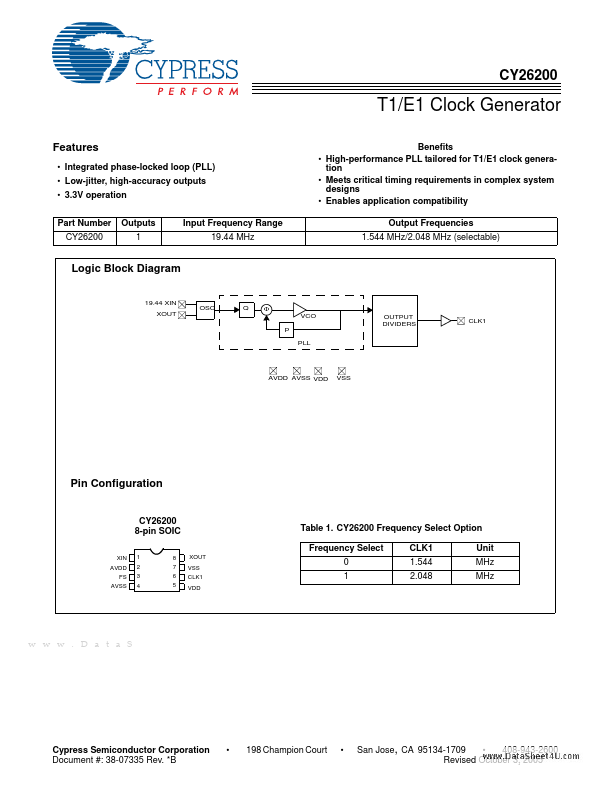

Logic Block Diagram

19.44 XIN XOUT

Φ VCO P PLL OUTPUT DIVIDERS CLK1

AVDD AVSS VDD

Pin Configuration

CY26200 8-pin SOIC

XIN AVDD FS AVSS 1 2 3 4 8 7 6 5 XOUT VSS CLK1 VDD

Table 1. CY26200 Frequency Select Option Frequency Select 0 1 CLK1 1.544 2.048 Unit MHz MHz w w w . D a t a S h e e t 4 U . c o m

Cypress Semiconductor Corporation Document #: 38-07335 Rev.

- B

- 198 Champion Court

- San Jose, CA 95134-1709

- 408-943-2600 Revised October 3, 2005

Pin Summary

Pin Name XIN AVDD FS AVSS VDD CLK1 VSS XOUT[1] Pin Number 1 2 3 4 5 6 7 8 19.44-MHz Reference Input Analog Voltage Supply...