CY26126

CY26126 is Dual Output 125-MHz Clock Generator manufactured by Cypress.

Advance Information

Dual Output 125-MHz Clock Generator

Features

- Integrated phase-locked loop

- Low skew, low jitter, high accuracy outputs

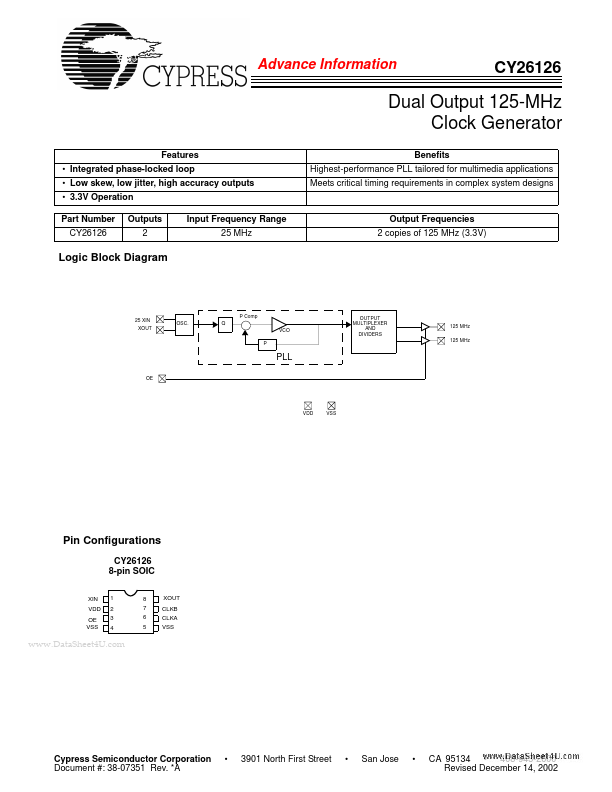

- 3.3V Operation Part Number CY26126 Outputs 2 Input Frequency Range 25 MHz Output Frequencies 2 copies of 125 MHz (3.3V) Benefits Highest-performance PLL tailored for multimedia applications Meets critical timing requirements in plex system designs

Logic Block Diagram

25 XIN XOUT

P p OSC. Q VCO P

OUTPUT MULTIPLEXER AND DIVIDERS

125 MHz 125 MHz

Pin Configurations

CY26126 8-pin SOIC

XIN VDD OE VSS 1 2 3 4 8 7 6 5 XOUT CLKB CLKA VSS

..

Cypress Semiconductor Corporation Document #: 38-07351 Rev.

- A

- 3901 North First Street

- San Jose

- CA 95134

- 408-943-2600 Revised December 14, 2002

Advance Information

Pin Summary

Name XIN VDD OE VSS VSS CLKA CLKB XOUT

[1]

Pin Number 1 2 3 4 5 6 7 8

Description Reference Input 3.3V Voltage Supply Output Enable Ground Ground 125-MHz Clock Output A 125-MHz Clock Output B Reference Output

Absolute Maximum Conditions

Parameter VDD TS TJ Storage Description Supply Voltage Temperature[2] Junction Temperature Digital Inputs Digital Outputs referred to VDD Electro-Static Discharge...