CY26049-22

CY26049-22 is Global Communications Clock Generator manufactured by Cypress.

Fail Safe™ Packet Clock™ Global munications Clock Generator

Features

- Fully integrated phase-locked loop (PLL)

- Fail Safe output

- PLL driven by a crystal oscillator that is phase aligned with external reference

- 100-MHz output from 10-MHz input

- Low-jitter, high-accuracy outputs

- 3.3V ± 5% operation

- 16-lead TSSOP

Benefits

- Integrated high-performance PLL tailored for telemunications frequency synthesis eliminates the need for external loop filter ponents

- When reference is off, DCXO maintains clock outputs and SAFE pin indicates Fail Safe conditions

- DCXO maintains continuous operation should the input reference clock fail

- Glitch-free transition simplifies system design

- Works with monly available, low-cost 10-MHz crystal

- Zero-ppm error for all output frequencies

- patible across industry standard design platforms

- Industry standard package with 6.4 × 5.0 mm2 footprint and a height profile of just 1.1 mm

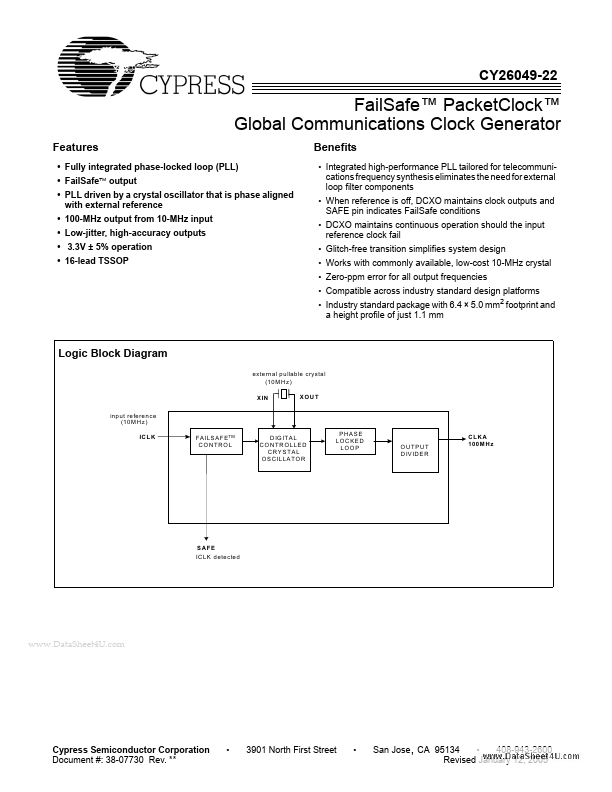

Logic Block Diagram e xte rn a l p u lla b le c rysta l (1 0 M H z ) X IN in p u t re fe re n ce (1 0 M H z ) IC L K F A IL S A F E TM CONTROL D IG IT A L C O N TR O LLE D CRYSTAL O S C IL L A T O R PHASE LO C K E D LO O P CLKA 100M H z XOUT

OUTPUT D IV ID E R

SAFE IC L K d e te cte d

..

Cypress Semiconductor Corporation Document #: 38-07730 Rev.

- -

- 3901 North First Street

- San Jose, CA 95134

- 408-943-2600 Revised January 12, 2005

Pin Configuration

16-pin TSSOP Top View

ICLK 1 NC 2 NC 3 NC 4 VDD 5 VSS 6 NC 7 XIN 8 16 NC 15 CLKA 14 NC 13 NC 12 VDD 11 VSS 10 SAFE 9...