CY26049-36

CY26049-36 is Global Communications Clock Generator manufactured by Cypress.

Fail Safe™ Packet Clock™ Global munications Clock Generator

Features

- Fully integrated phase-locked loop (PLL)

- Fail Safe output

- PLL driven by a crystal oscillator that is phase aligned with external reference

- Output frequencies selectable and/or programmed to standard munication frequencies

- Low-jitter, high-accuracy outputs

- mercial and Industrial operation

- 3.3V ± 5% operation

- 16-lead TSSOP

- When reference is in range, SAFE pin is driven high.

- When reference is off, DCXO maintains clock outputs. SAFE pin is low.

- DCXO maintains continuous operation should the input reference clock fail

- Glitch-free transition simplifies system design

- Selectable output clock rates include T1/DS1, E1, T3/DS3, E3, and OC-3.

- Works with monly available, low-cost 18.432-MHz crystal

- Zero-ppm error for all output frequencies

- Performance guaranteed for applications that require an extended temperature range

- patible across industry standard design platforms

- Industry standard package with 6.4 x 5.0 mm2 footprint and a height profile of just 1.1 mm.

Benefits

- Integrated high-performance PLL tailored for telemunications frequency synthesis eliminates the need for external loop filter ponents

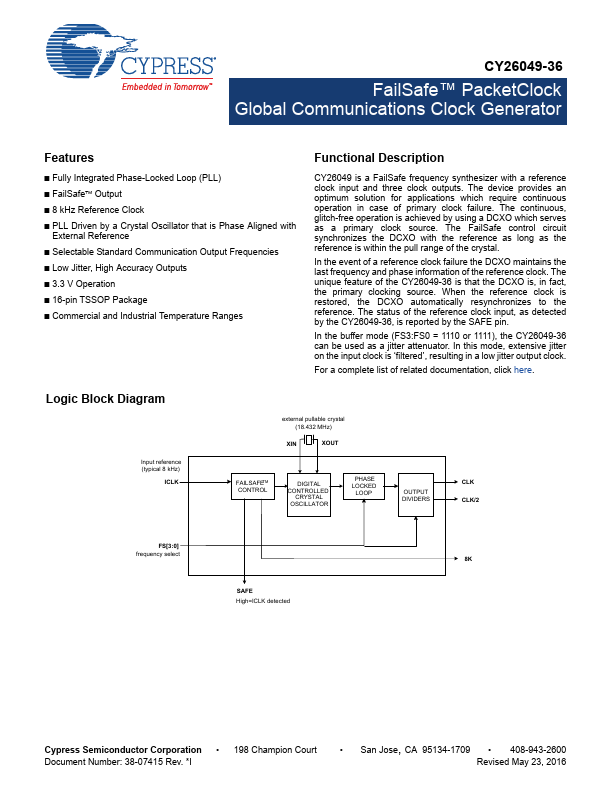

Logic Block Diagram external pullable crystal (18.432 MHz) XIN Input reference (typical 8 k Hz) ICLK

TM FAILSAFE CONTROL

XOUT

DIGITAL CONTROLLED CRYSTAL OSCILLATOR

PHASE LOCKED LOOP

CLK OUTPUT DIVIDERS CLK/2

FS[3:0] frequency...