CY7C1347D Overview

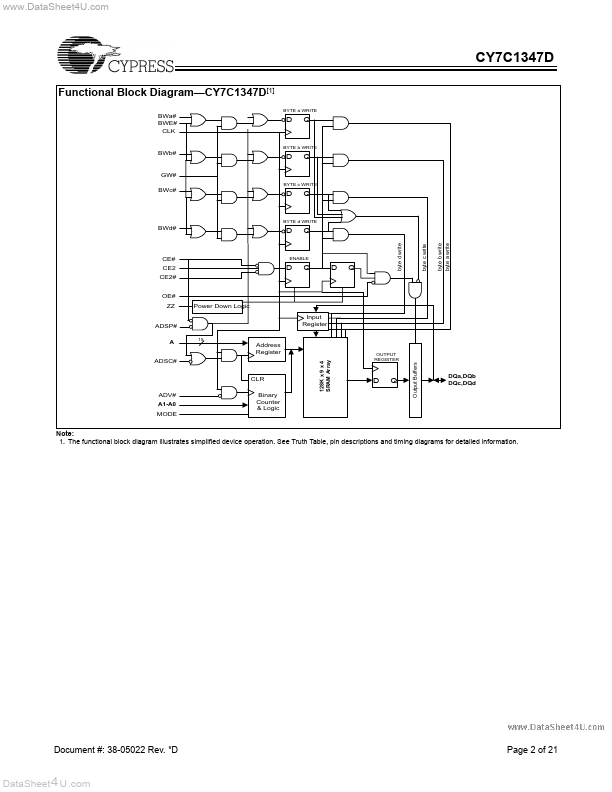

This Cypress Synchronous Burst SRAM employs high-speed, low-power CMOS designs using advanced triple-layer polysilicon, double-layer metal technology. Each memory cell consists of four transistors and two high-valued resistors. The CY7C1347D SRAM integrate 131,072 x 36 SRAM cells with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation.

CY7C1347D Key Features

- Fast access times: 2.5 and 3.5 ns

- Fast clock speed: 250, 225, 200, and 166 MHz

- 1.5-ns set-up time and 0.5-ns hold time

- Fast OE access times: 2.5 ns and 3.5 ns

- Optimal for depth expansion (one cycle chip deselect to eliminate bus contention)

- 3.3V -5% and +10% power supply

- 3.3V or 2.5V I/O supply

- 5V tolerant inputs except I/Os

- Clamp diodes to VSS at all inputs and outputs

- mon data inputs and data outputs