CY7C13451G Overview

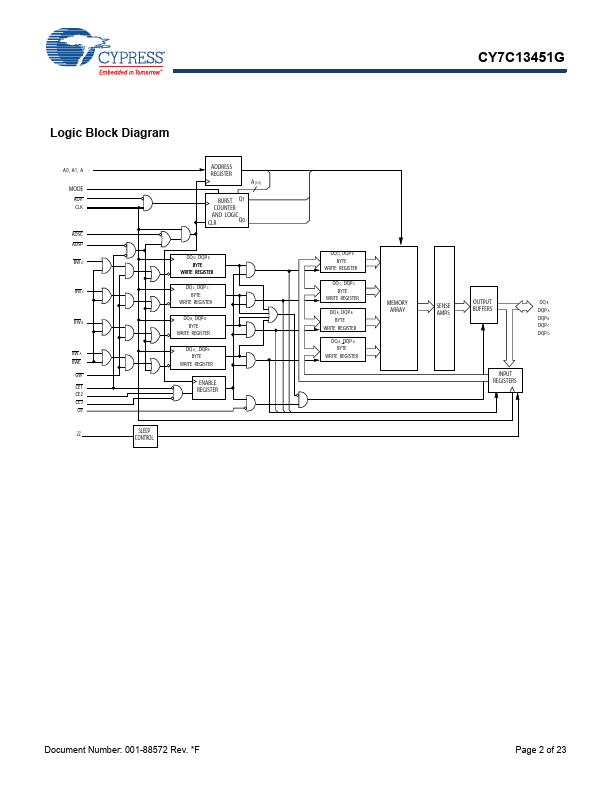

Functional Description The CY7C13451G is a 128K × 36 synchronous cache RAM designed to interface with high speed microprocessors with minimum glue logic. The maximum access delay from clock rise is 8.0 ns (100 MHz version). A 2 bit on-chip counter captures the first address in a burst and inc.

CY7C13451G Key Features

- 128K × 36 mon I/O

- 3.3 V core Power Supply (VDD)

- 2.5 V or 3.3 V I/O Supply (VDDQ)

- Fast Clock-to-output times

- 8.0 ns (100 MHz version)

- Provide high performance 2-1-1-1 access rate

- User selectable burst counter supporting Intel Pentium

- Separate Processor and Controller Address Strobes

- Synchronous Self Timed Write

- Asynchronous output enable