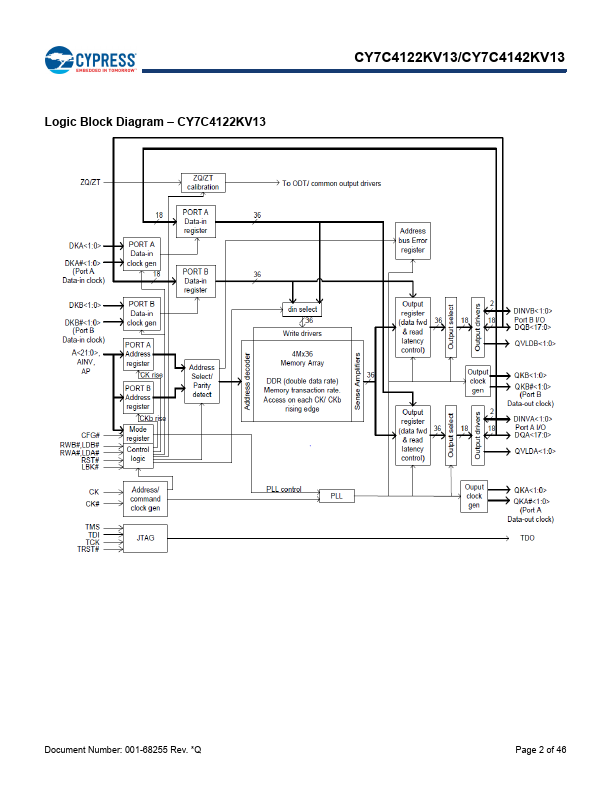

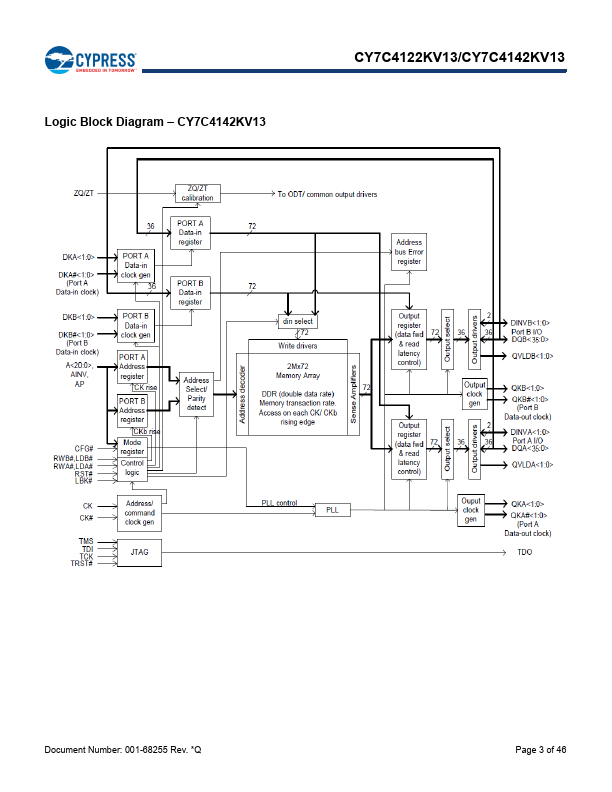

CY7C4122KV13 Overview

The QDR™-IV XP (Xtreme Performance) SRAM is a high-performance memory device optimized to maximize the number of random transactions per second by the use of two independent bidirectional data ports. These ports are equipped with DDR interfaces and designated as port A and port B respectively. Accesses to these two data ports are concurrent and independent of each other.

CY7C4122KV13 Key Features

- 144-Mbit density (8M × 18, 4M × 36)

- Total Random Transaction Rate[1] of 2132 MT/s

- Maximum operating frequency of 1066 MHz

- Read latency of 8.0 clock cycles and write latency of 5.0 clock cycles

- Eight-bank architecture enables one access per bank per cycle

- Two-word burst on all accesses

- Dual independent bidirectional data ports

- Double data rate (DDR) data ports

- Supports concurrent read/write transactions on both ports

- Single address port used to control both data ports