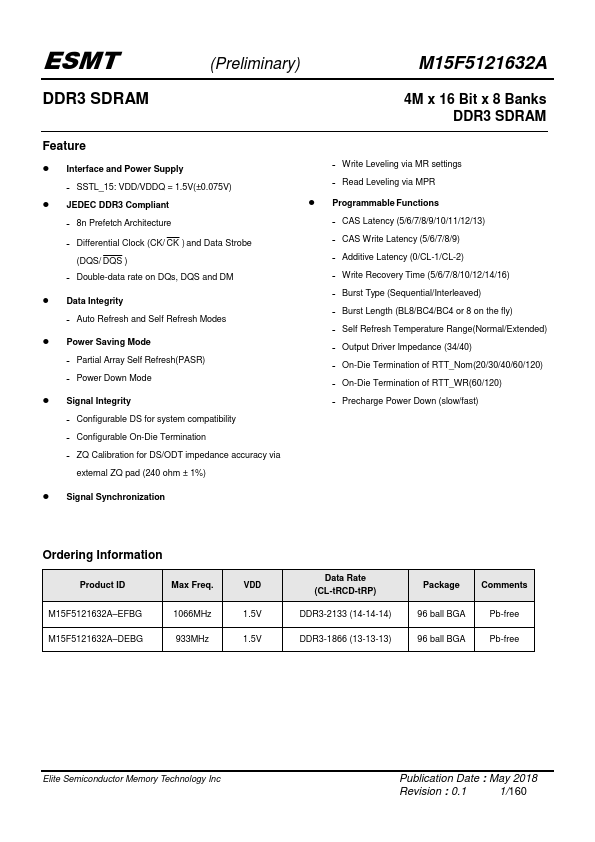

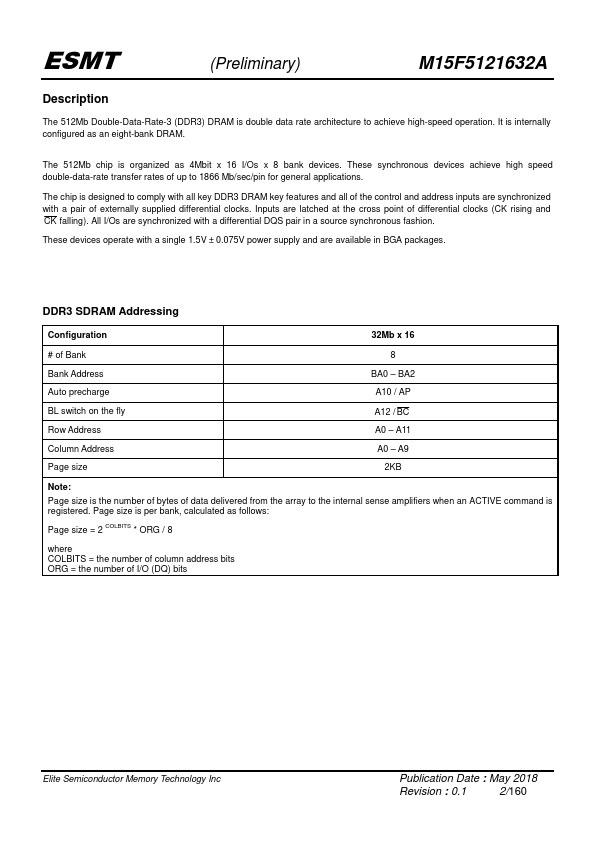

M15F5121632A Description

The 512Mb Double-Data-Rate-3 (DDR3) DRAM is double data rate architecture to achieve high-speed operation. It is internally configured as an eight-bank DRAM. The 512Mb chip is organized as 4Mbit x 16 I/Os x 8 bank devices.

M15F5121632A Key Features

- ORG / 8