HD74ALVCH16825

Description

The HD74ALVCH16825 improves the performance and density of 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The device can be used as two 9-bit buffers or one 18bit buffer. It provides true data. The 3-state control gate is a 2-input AND gate with active low inputs so that if either output enable (OE1 or OE2) input is high, all nine affected outputs are in the high impedance state. Active bus hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

Features

- VCC = 2.3 V to 3.6 V

- Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

- Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C)

- High output current ±24 m A (@V CC = 3.0 V)

- Bus hold on data inputs eliminates the need for external pullup / pulldown resistors

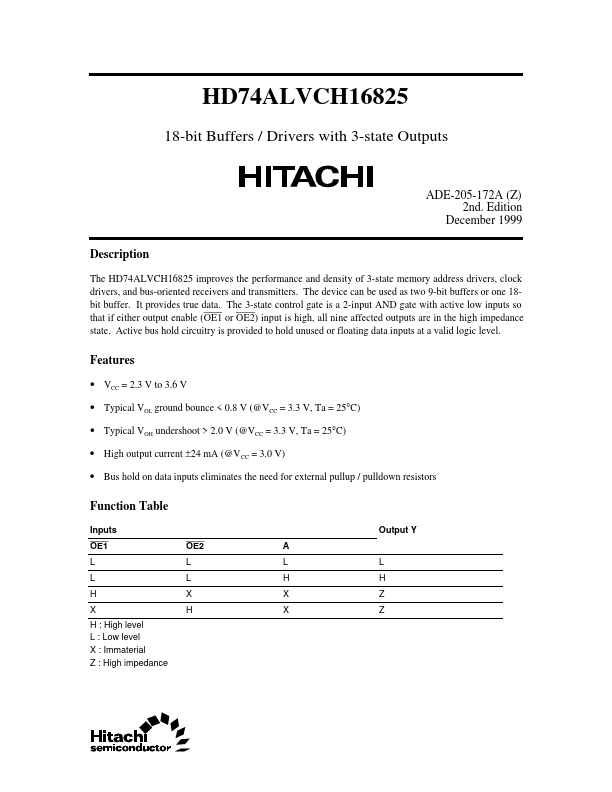

Function Table

Inputs OE1 L L H X H : High level L : Low level X : Immaterial Z : High impedance OE2 L L X H A L H X X L H Z Z Output Y

Pin Arrangement

1OE...