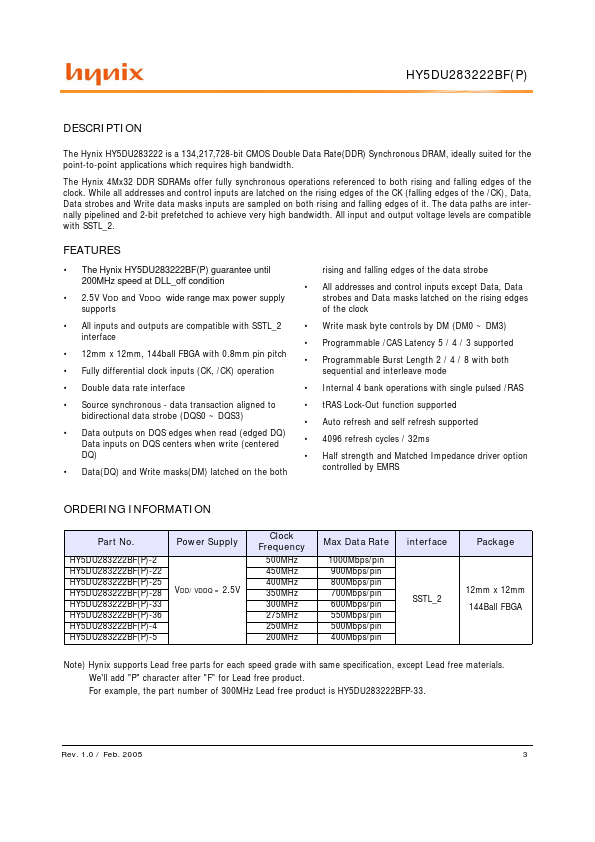

HY5DU283222BF Description

and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for use of circuits described. No patent licenses are implied.

HY5DU283222BF Key Features

- The Hynix HY5DU283222BF(P) guarantee until 200MHz speed at DLL_off condition

- 2.5V VDD and VDDQ wide range max power supply supports

- All inputs and outputs are patible with SSTL_2 interface

- 12mm x 12mm, 144ball FBGA with 0.8mm pin pitch

- Fully differential clock inputs (CK, /CK) operation

- Double data rate interface

- Source synchronous

- data transaction aligned to bidirectional data strobe (DQS0 ~ DQS3)

- Data outputs on DQS edges when read (edged DQ) Data inputs on DQS centers when write (centered DQ)

- Data(DQ) and Write masks(DM) latched on the both