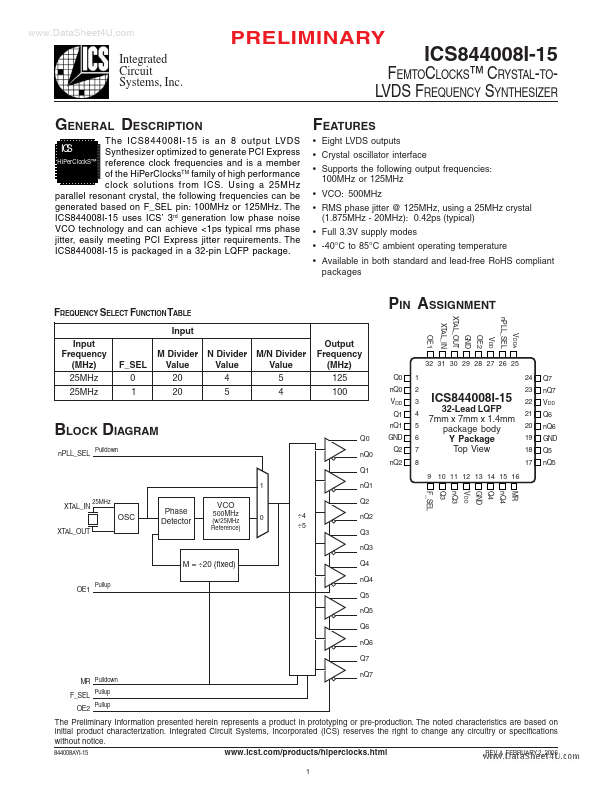

ICS844008I-15

Overview

The ICS844008I-15 is an 8 output LVDS Synthesizer optimized to generate PCI Express HiPerClockS™ reference clock frequencies and is a member of the HiPerClocksTM family of high performance clock solutions from ICS. Using a 25MHz parallel resonant crystal, the following frequencies can be generated based on F_SEL pin: 100MHz or 125MHz.

- Eight LVDS outputs

- Crystal oscillator interface

- Supports the following output frequencies: 100MHz or 125MHz

- VCO: 500MHz

- RMS phase jitter @ 125MHz, using a 25MHz crystal (1.875MHz - 20MHz): 0.42ps (typical)

- Full 3.3V supply modes

- -40°C to 85°C ambient operating temperature

- Available in both standard and lead-free RoHS compliant packages