ICS542 Key Features

- Packaged as 8 pin SOIC

- ICS’ lowest cost clock divider

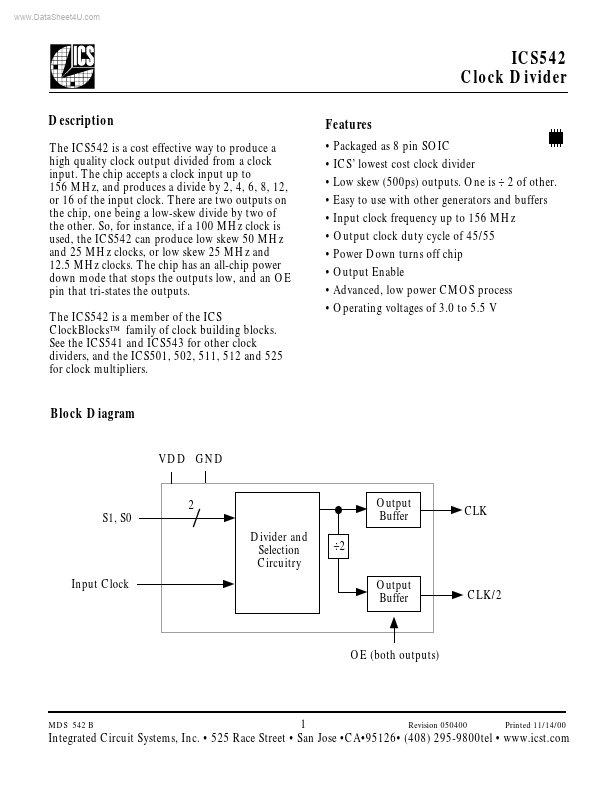

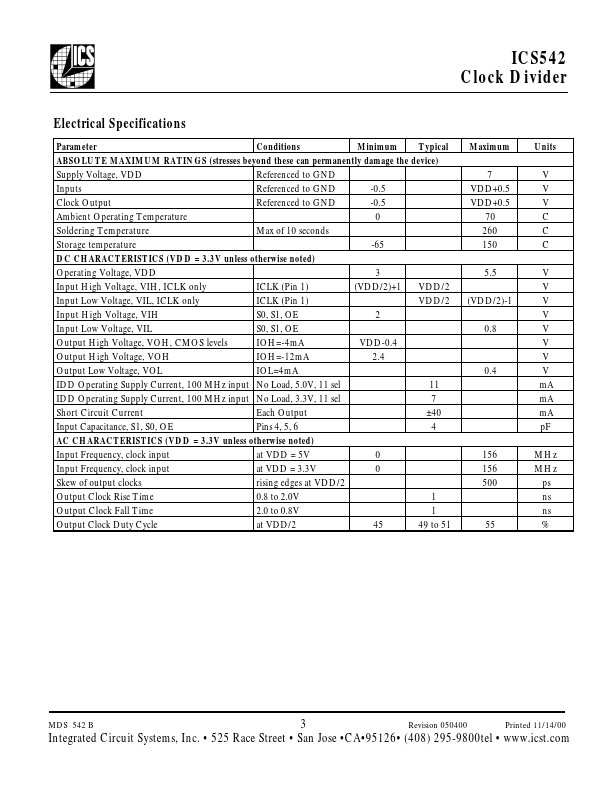

- Low skew (500ps) outputs. One is ÷ 2 of other

- Easy to use with other generators and buffers

- Input clock frequency up to 156 MHz

- Output clock duty cycle of 45/55

- Power Down turns off chip

- Output Enable

- Advanced, low power CMOS process

- Operating voltages of 3.0 to 5.5 V