Datasheet Summary

..

PRELIMINARY INFORMATION

I C R O C LOC K

Description

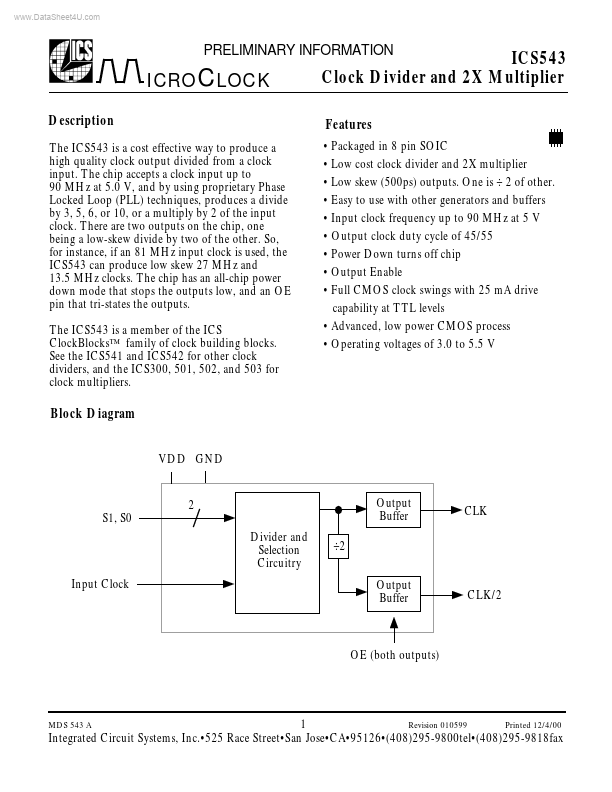

The ICS543 is a cost effective way to produce a high quality clock output divided from a clock input. The chip accepts a clock input up to 90 MHz at 5.0 V, and by using proprietary Phase Locked Loop (PLL) techniques, produces a divide by 3, 5, 6, or 10, or a multiply by 2 of the input clock. There are two outputs on the chip, one being a low-skew divide by two of the other. So, for instance, if an 81 MHz input clock is used, the ICS543 can produce low skew 27 MHz and 13.5 MHz clocks. The chip has an all-chip power down mode that stops the outputs low, and an OE pin that tri-states the outputs. The ICS543 is a member...