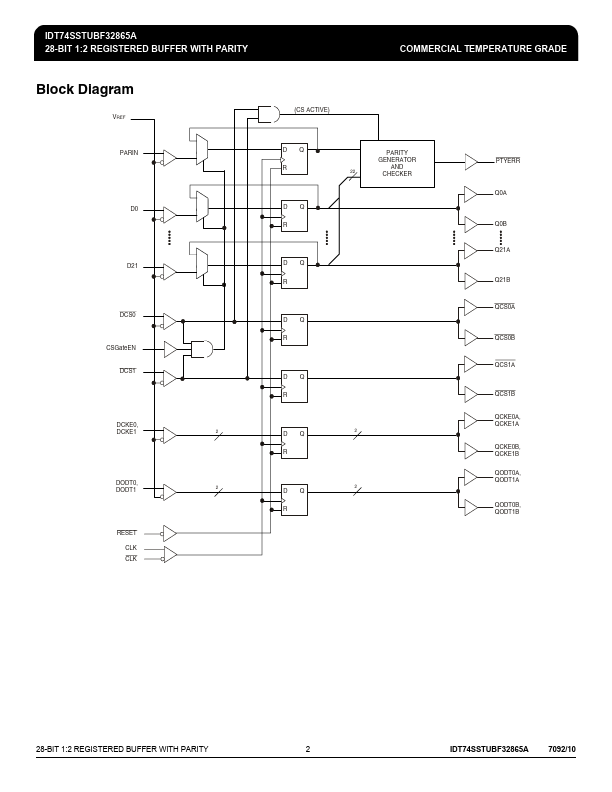

ICSSSTUAF32865A Overview

This 28-bit 1:2 registered buffer with parity is designed for 1.7V to 1.9V VDD operation. All clock and data inputs are patible with the JEDEC standard for SSTL_18. The control inputs are LVCMOS.

ICSSSTUAF32865A Key Features

- 28-bit 1:2 registered buffer with parity check functionality

- Supports SSTL_18 JEDEC specification on data inputs

- and outputs Supports LVCMOS switching levels on CSGateEN and RESET inputs Low voltage operation: VDD = 1.7V to 1.9V Avai