- Part: IDT71V25781

- Description: Synchronous SRAMs

- Manufacturer: IDT

- Size: 539.14 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

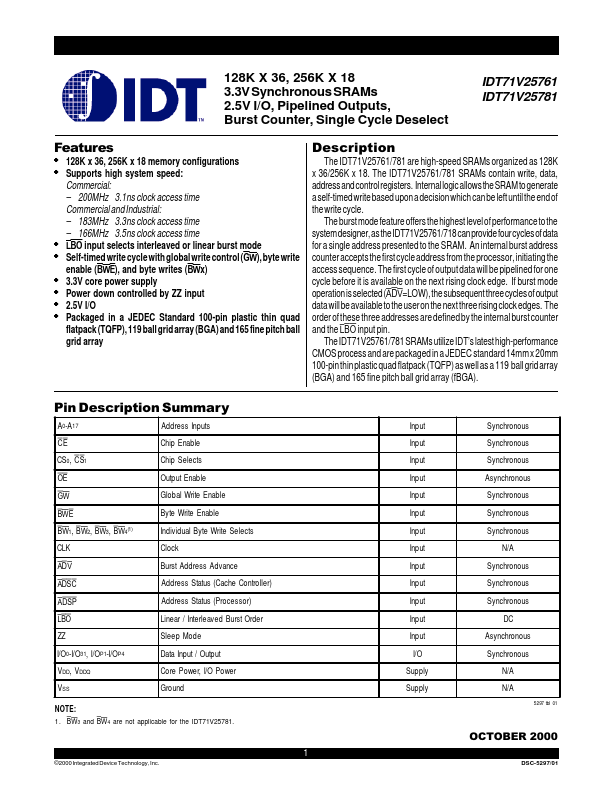

| IDT71V2578S | Integrated Device Technology | 128K X 36/ 256K X 18 3.3V Synchronous SRAMs 2.5V I/O/ Pipelined Outputs/ Burst Counter/ Single Cycle Deselect |

| IDT71V2578SA | Integrated Device Technology | 128K X 36/ 256K X 18 3.3V Synchronous SRAMs 2.5V I/O/ Pipelined Outputs/ Burst Counter/ Single Cycle Deselect |