ICS571 Description

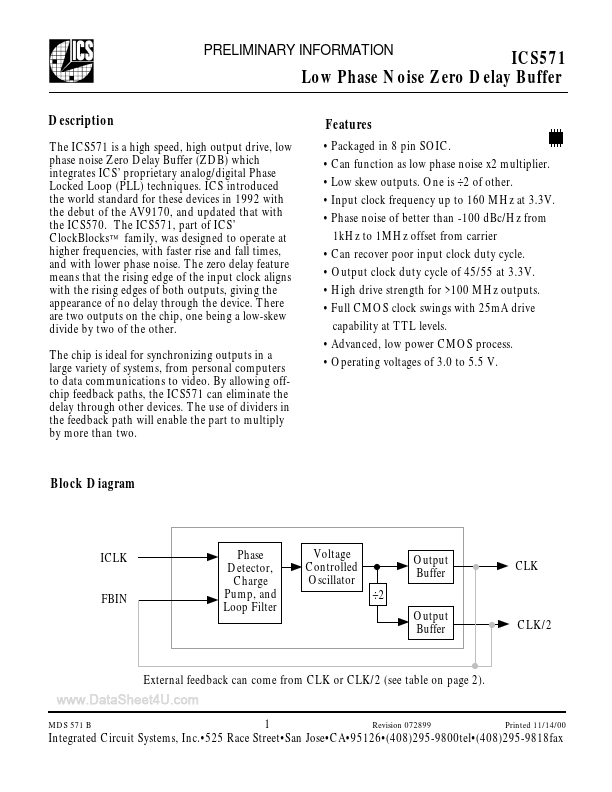

The ICS571 is a high speed, high output drive, low phase noise Zero Delay Buffer (ZDB) which integrates ICS’ proprietary analog/digital Phase Locked Loop (PLL) techniques. ICS introduced the world standard for these devices in 1992 with the debut of the AV9170, and updated that with the ICS570. The ICS571, part of ICS’ ClockBlocks™ family, was designed to operate at higher frequencies, with faster rise and fall...

ICS571 Key Features

- Packaged in 8 pin SOIC

- Can function as low phase noise x2 multiplier

- Low skew outputs. One is ÷2 of other

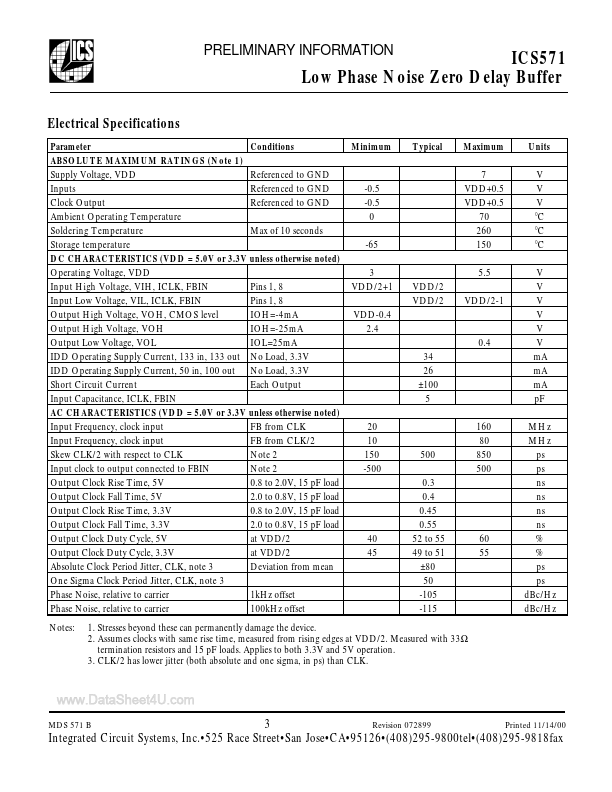

- Input clock frequency up to 160 MHz at 3.3V

- Phase noise of better than -100 dBc/Hz from 1kHz to 1MHz offset from carrier

- Can recover poor input clock duty cycle

- Output clock duty cycle of 45/55 at 3.3V

- High drive strength for >100 MHz outputs

- Full CMOS clock swings with 25mA drive capability at TTL levels

- Advanced, low power CMOS process