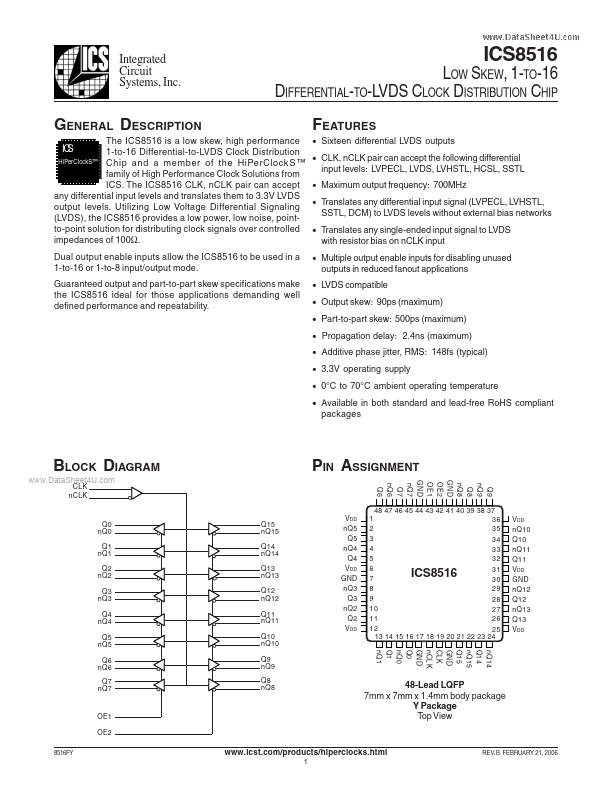

ICS8516 Description

The ICS8516 is a low skew, high performance 1-to-16 Differential-to-LVDS Clock Distribution HiPerClockS™ Chip and a member of the HiPerClock S ™ family of High Performance Clock Solutions from ICS. The ICS8516 CLK, nCLK pair can accept any differential input levels and translates them to 3.3V LVDS output levels. Utilizing Low Voltage Differential Signaling (LVDS), the ICS8516 provides a low power, low noise,...

ICS8516 Key Features

- Sixteen differential LVDS outputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 700MHz

- Translates any differential input signal (LVPECL, LVHSTL, SSTL, DCM) to LVDS levels without external bias networks

- Translates any single-ended input signal to LVDS with resistor bias on nCLK input

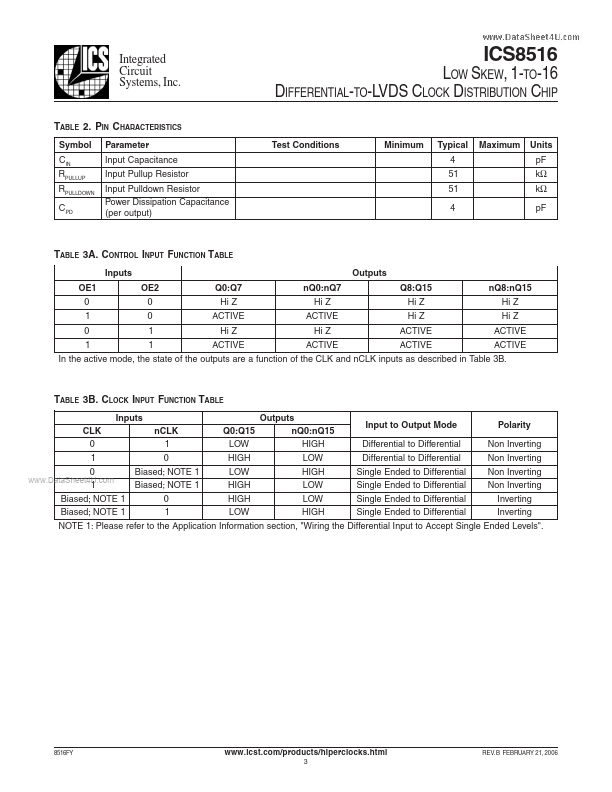

- Multiple output enable inputs for disabling unused outputs in reduced fanout